Department of Electrical & Computer Engineering

# Microwind & Dsch User's Manual Version 2.7

November 2003 Etienne Sicard

http://www.microwind.org

MICROWIND & DSCH V2.7 - USER'S MANUAL

1. Introduction

#### About the author

ETIENNE SICARD was born in Paris, France, in June 1961. He received a B.S degree in 1984 and a PhD in Electrical Engineering in 1987 both from the University of Toulouse. He was granted a Monbusho scholarship and stayed 18 months at the University of Osaka, Japan. Previously a professor of electronics in the department of physics, at the University of Balearic Islands, Spain, E. Sicard is currently a professor at the INSA Electronic Engineering School of Toulouse. His research interests include several aspects of design of integrated circuits including crosstalk fault tolerance, and electromagnetic compatibility of integrated circuits. Etienne SICARD is the author of several commercial software in the field of microelectronics and sound processing.

#### Copyright

© Copyright 1997-2004 by INSA

#### **Address**

Etienne Sicard INSA-DGEI, 135, Av de Rangueil 31077 TOULOUSE Cedex 4, FRANCE

Tel: +33.561.55.98.42, Fax: +33.561.55.98.00

e-mail: etienne.sicard@insa-tlse.fr

home page: http://intrage.insa-tlse.fr/~etienne

#### Web information

http://www.microwind.org

#### **Acknowledgements**

Special thanks are due to technical contributors to the Dsch and Microwind software, to numerous professors, students and engineers who patiently debugged the software, gave valuable comments and suggestions. I would like to thank several people at INSA, especially Sonia Bendhia and Chen Xi, Jean-Pierre Schoellkopf, Fabrizzio Battaglia at ST-Microelectronics, and Bernard Courtois, Tima Grenoble, for their help, support and contributions. Also, I would like to thank Marie-Agnes Detourbe for having carefully reviewed the manuscript. This software is dedicated to John Uyemura, from Georgia Tech, Usa, who was an unconditional fan of Microwind.

ISBN 2-87649-046-3

# **Table of Contents**

| 1 | Int  | roduction & Installation                  | <i>7</i> |

|---|------|-------------------------------------------|----------|

|   | INST | FALLATION                                 | 8        |

| 2 | Teo  | chnology Scale Down                       | 9        |

| _ | 2.1  | Evolution of Microprocessors and Memories | 9        |

|   | 2.2  | Frequency Improvements                    |          |

|   | 2.3  | Increased Layers                          |          |

|   | 2.4  | Design Trends                             |          |

|   | 2.5  | Exercises                                 |          |

| 3 | The  | e MOS device                              |          |

|   | 3.1  | Logic Levels                              |          |

|   | 3.2  | The MOS as a switch                       |          |

|   | 3.3  | Logic Simulation of the MOS.              |          |

|   | 3.4  | MOS layout                                |          |

|   | 3.5  | Vertical aspect of the MOS                |          |

|   | 3.6  | Static Mos Characteristics                |          |

|   | 3.7  | Dynamic MOS behavior                      |          |

|   | 3.8  | Analog Simulation                         |          |

|   | 3.9  | Layout considerations                     |          |

|   | 3.10 | The MOS Model 1                           |          |

|   | 3.11 | The MOS Model 3                           |          |

|   | 3.12 | The BSIM4 MOS Model                       |          |

|   | 3.13 | Low leakage MOS                           |          |

|   | 3.14 | High voltage MOS                          |          |

|   | 3.15 | Temperature effects on the MOS            |          |

|   | 3.16 | The PMOS Transistor                       |          |

|   | 3.17 | Process Variations                        |          |

|   | 3.18 | The Transmission Gate                     |          |

| 4 | The  | e Inverter                                | 33       |

|   | 4.1  | The Logic Inverter                        |          |

|   | 4.2  | THE CMOS INVERTER                         |          |

|   | 4.3  | MANUAL LAYOUT OF THE INVERTER             | 35       |

|   | 4.4  | Connection between Devices                | 35       |

|   | 4.5  | Useful Editing Tools                      |          |

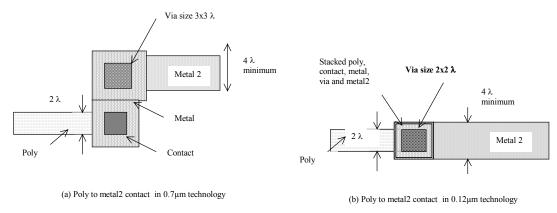

|   | 4.6  | Metal-to-poly                             |          |

|   | 4.7  | Supply Connections                        |          |

|   | 4.8  | Process steps to build the Inverter       |          |

|   | 4.9  | Inverter Simulation                       |          |

|   | 4.10 | 3-STATE INVERTER                          |          |

|   | 4.11 | Exercises                                 |          |

| 5 | Bas  | sic Gates                                 |          |

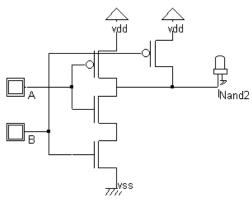

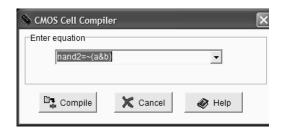

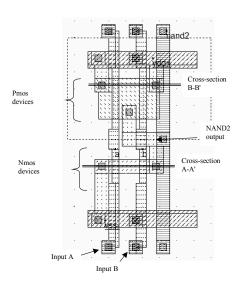

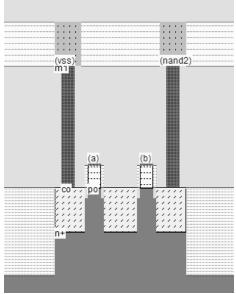

|   | 5.1  | Introduction                              | 43       |

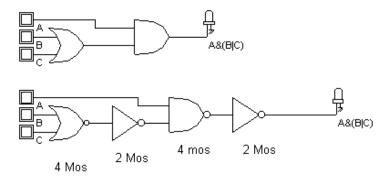

|   | 5.2  | The Nand Gate                             | 43       |

|   | 5 3  | The AND gate                              | 45       |

#### 1. Introduction

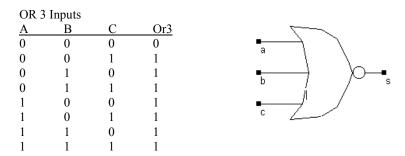

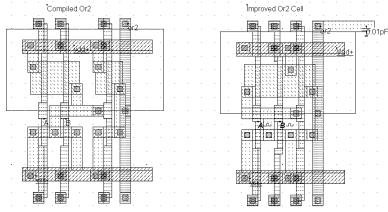

|   | 5.4   | The 3-Input OR Gate                            |     |

|---|-------|------------------------------------------------|-----|

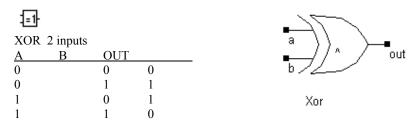

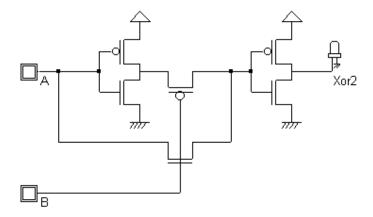

|   | 5.5   | The XOR Gate                                   | 47  |

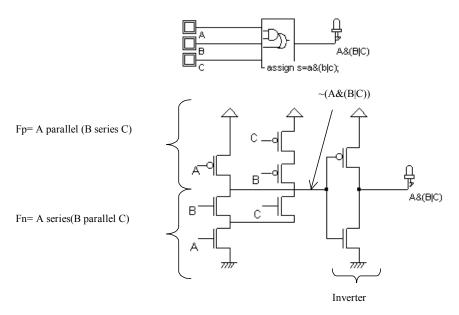

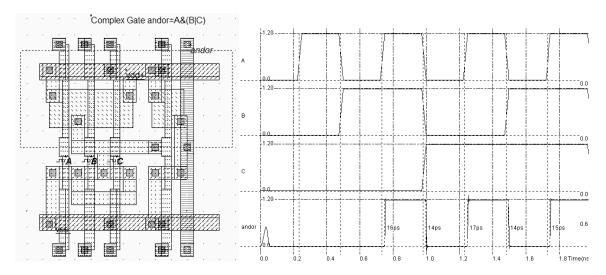

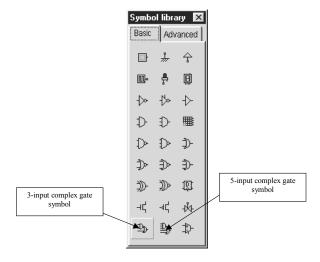

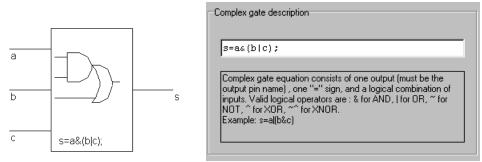

|   | 5.6   | Complex Gates                                  | 48  |

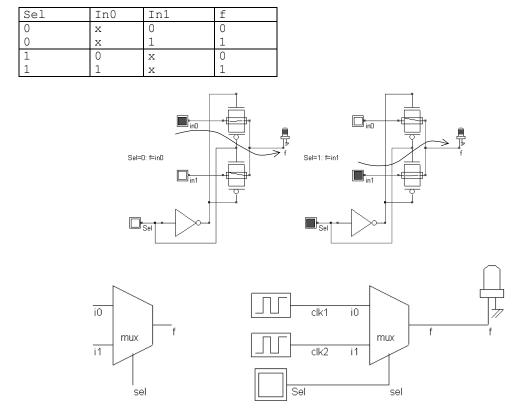

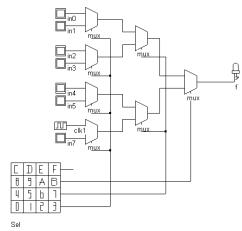

|   | 5.7   | Multiplexor                                    |     |

|   | 5.8   | 8 to 1 Multiplexor                             | 52  |

|   | 5.9   | Interconnects and Vias                         | 52  |

|   | 5.10  | Exercises                                      | 55  |

| 6 | Ari   | ithmetics                                      | 56  |

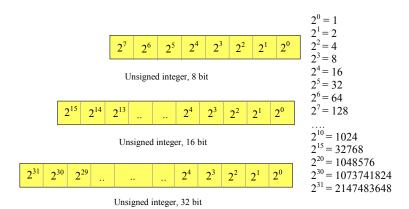

| U | 6.1   | Unsigned Integer format                        |     |

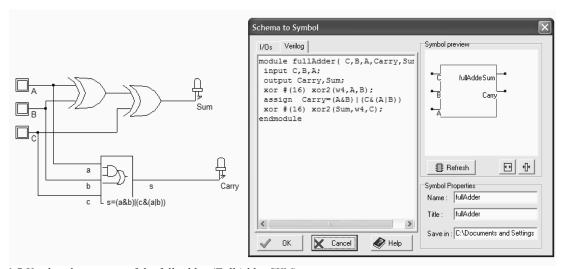

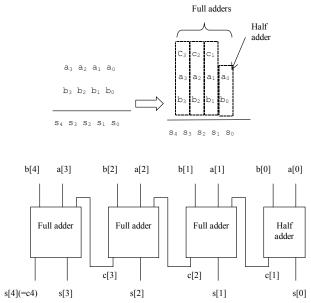

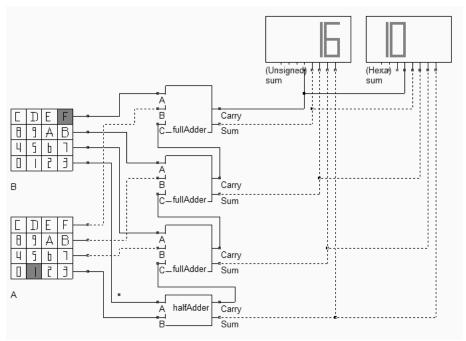

|   | 6.2   | Creating Arithmetic Circuits From Logic Design |     |

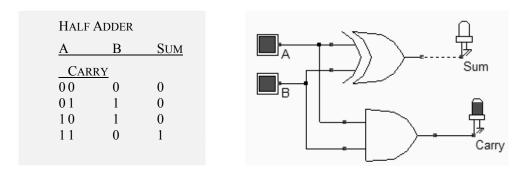

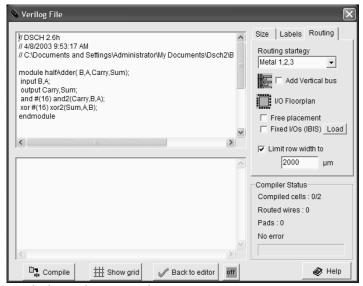

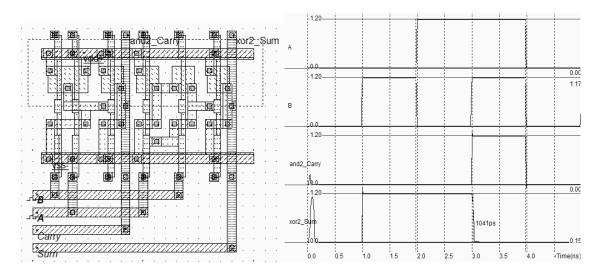

|   | 6.3   | Half-Adder Gate                                |     |

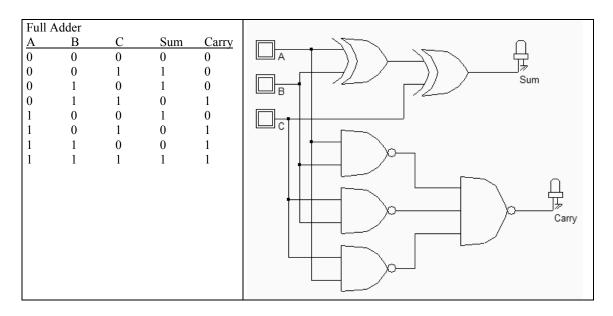

|   | 6.4   | Full-Adder Gate                                |     |

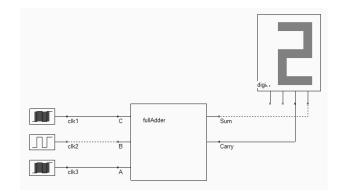

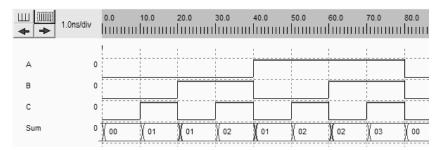

|   | 6.5   | Full-Adder Symbol in DSCH                      |     |

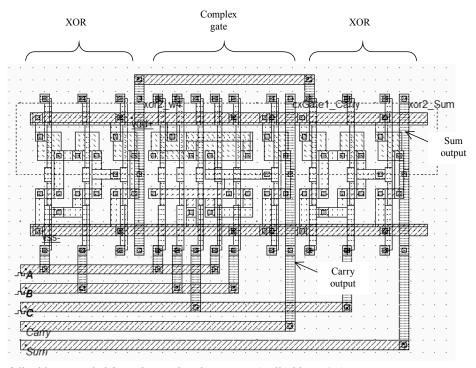

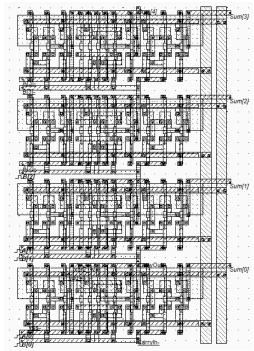

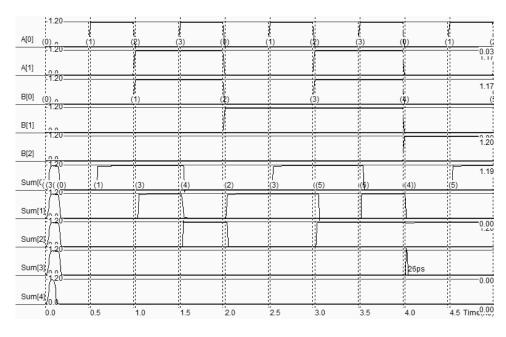

|   | 6.6   | Full-Adder Layout                              |     |

|   | 6.7   | Four-Bit Adder                                 |     |

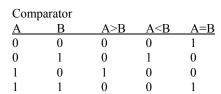

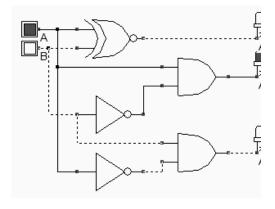

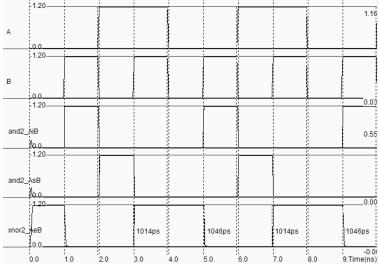

|   | 6.8   | Comparator                                     |     |

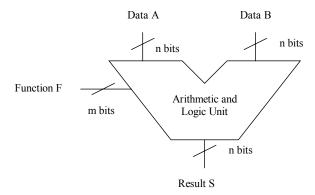

|   | 6.9   | Arithmetic and Logic Unit                      |     |

|   | 6.10  | Model of the PIC 16f84                         |     |

|   |       |                                                |     |

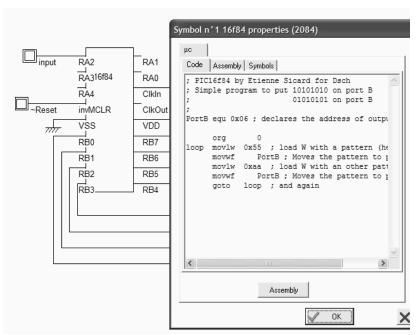

| 7 |       | tches                                          |     |

|   | 7.1   | Basic Latch                                    |     |

|   | 7.2   | RS Latch                                       |     |

|   | 7.3   | D Latch                                        |     |

|   | 7.4   | Edge Trigged Latch                             |     |

|   | 7.5   | Counter                                        | 78  |

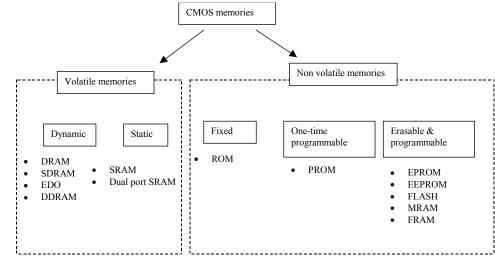

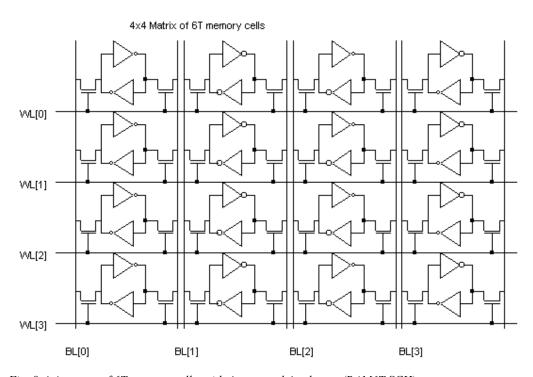

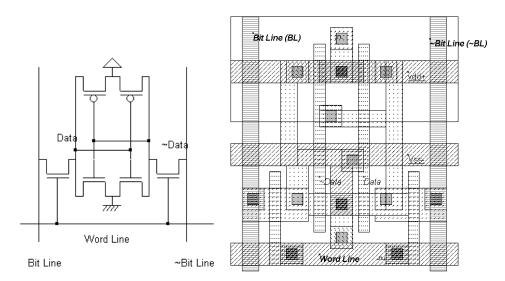

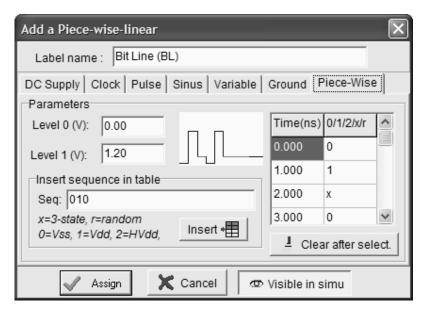

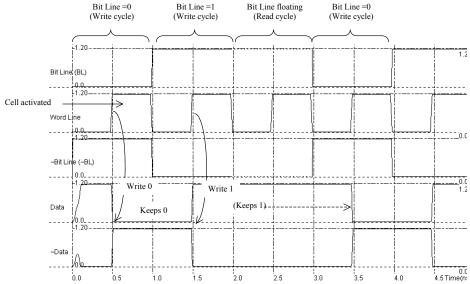

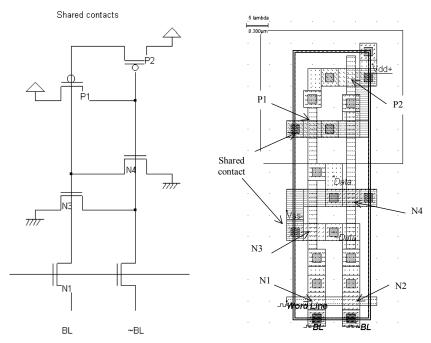

| 8 | Me    | emory Circuits                                 |     |

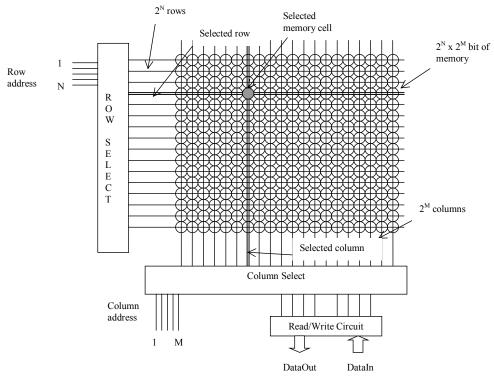

| - | 8.1   | The world of Memory                            |     |

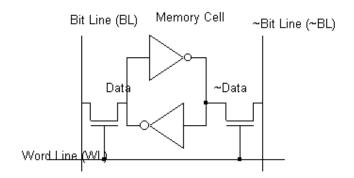

|   | 8.2   | RAM Memory                                     |     |

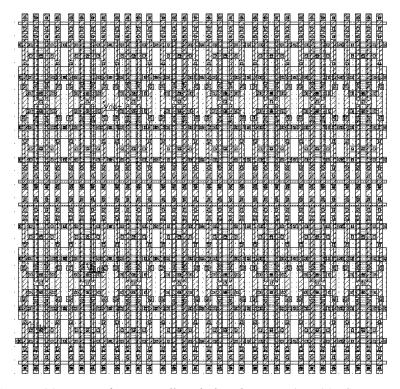

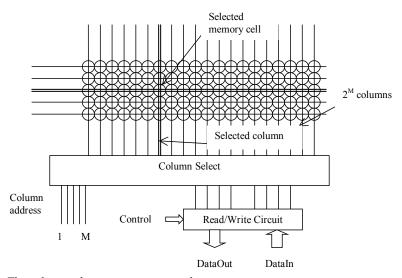

|   | 8.3   | RAM Array                                      |     |

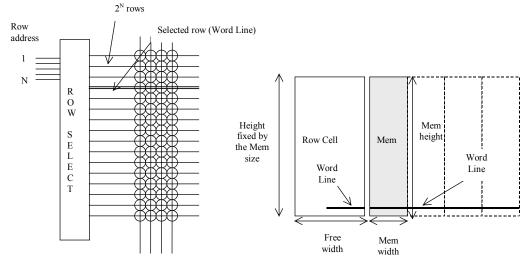

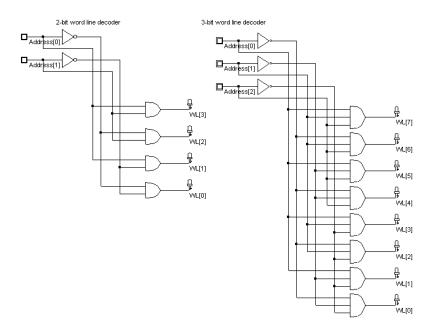

|   | 8.4   | Row Selection Circuit                          |     |

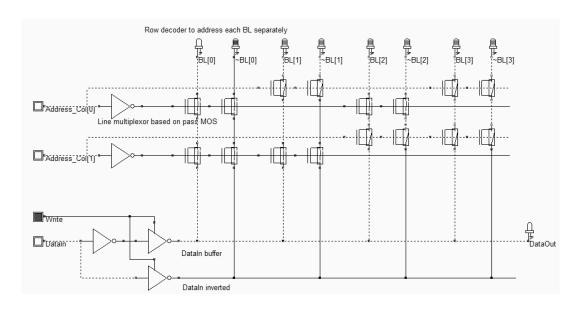

|   | 8.5   | Column Selection Circuit                       |     |

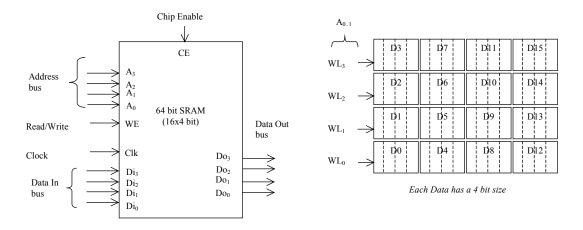

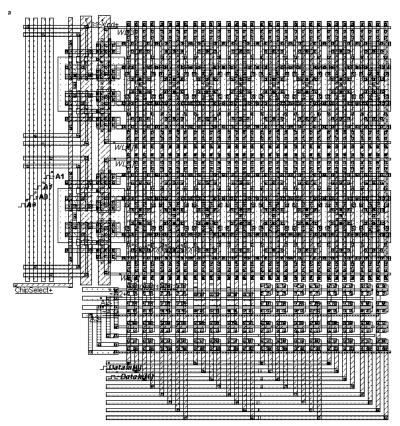

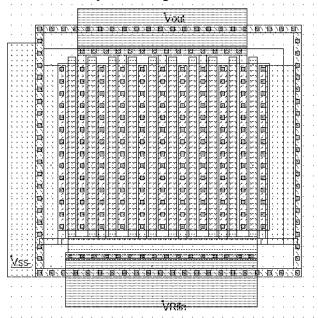

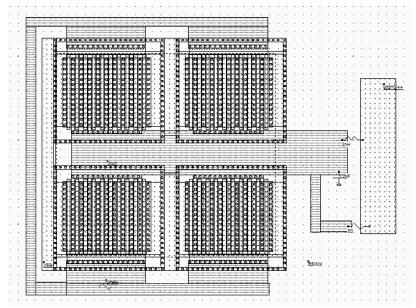

|   | 8.6   | A Complete 64 bit SRAM                         | 87  |

|   | 8.7   | Dynamic RAM Memory                             | 88  |

|   | 8.8   | EEPROM                                         | 91  |

|   | 8.8.  | .1 Double-gate MOS Charge                      | 92  |

|   | 8.8.2 | .2 Double-gate MOS Discharge                   | 93  |

|   | 8.9   | Flash Memories                                 |     |

|   | 8.10  | Ferroelectric RAM memories                     |     |

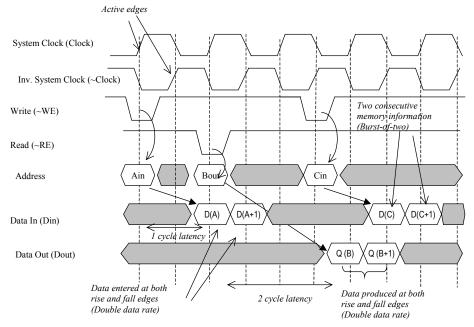

|   | 8.11  | Memory Interface                               |     |

|   | 8.12  | EXERCISES                                      |     |

| ^ | 4     |                                                | 404 |

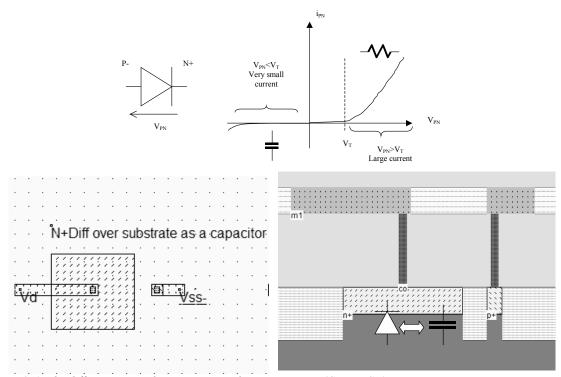

| 9 |       | alog Cells                                     |     |

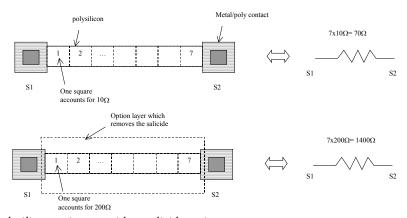

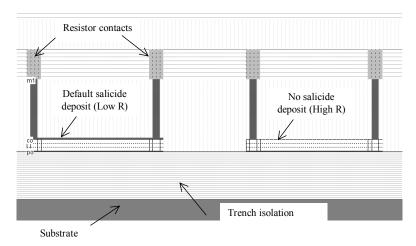

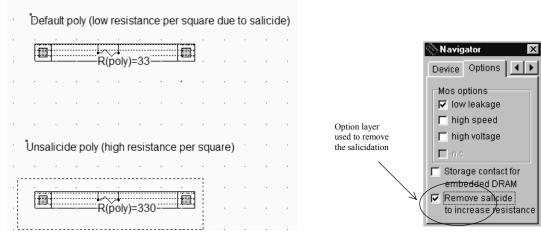

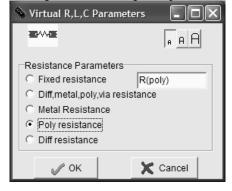

|   | 9.1   | Resistor                                       |     |

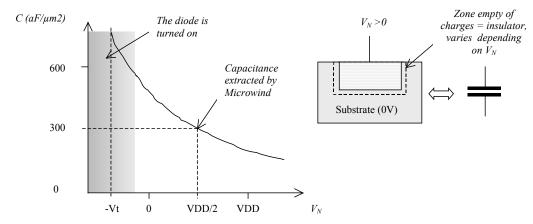

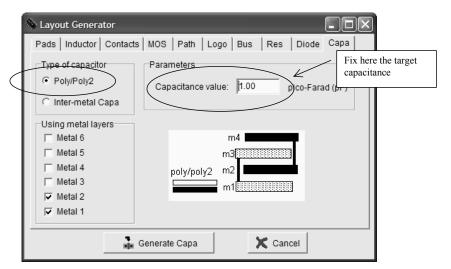

|   | 9.2   | Capacitor                                      |     |

|   | 9.2.  | 1                                              |     |

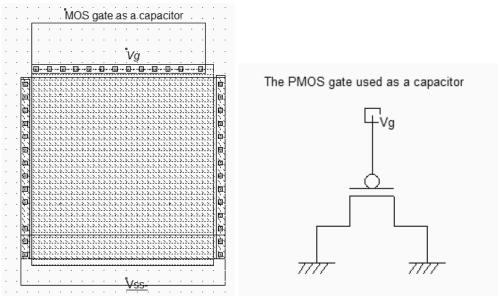

|   | 9.3   | Mos Capacitor                                  |     |

|   | 9.4   | Poly-Poly2 Capacitor                           |     |

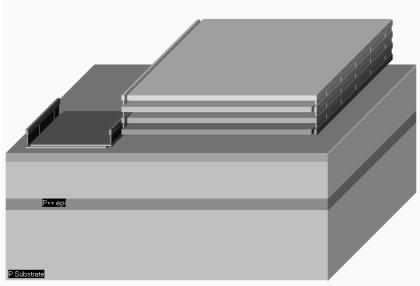

|   | 9.5   | Inter-Metal Capacitor                          |     |

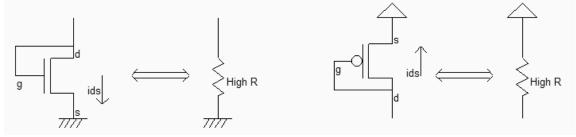

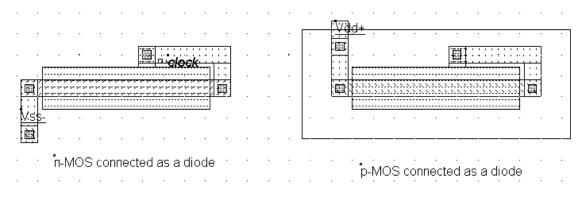

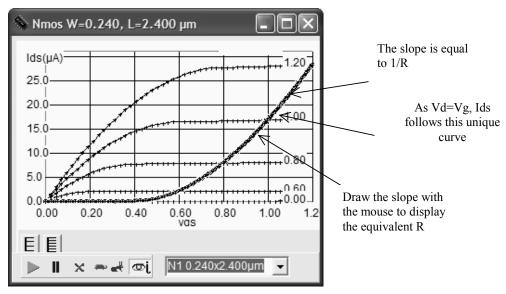

|   | 9.6   | Diode-connected MOS                            |     |

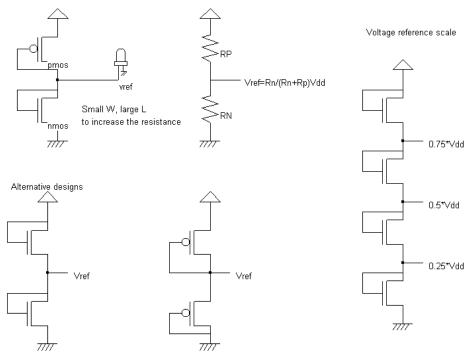

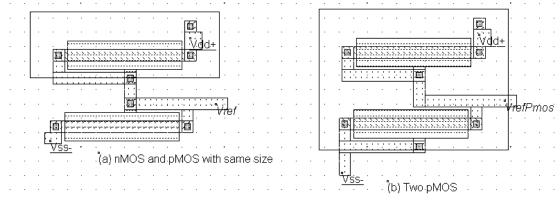

|   | 9.7   | Voltage Reference                              |     |

|   | 9.8   | Current mirror                                 |     |

|   | 9.9   | Amplifier                                      |     |

|   | 9.10  | Simple Differential Amplifier                  | 11/ |

#### 1. Introduction

| 9.11<br>9.12 | Push-Pull Amplifier Exercises                    |     |

|--------------|--------------------------------------------------|-----|

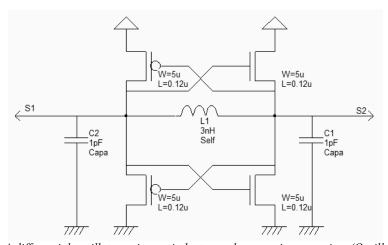

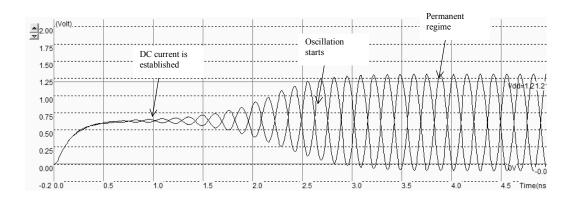

|              | Radio Frequency Circuits                         |     |

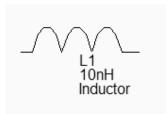

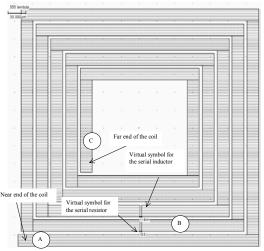

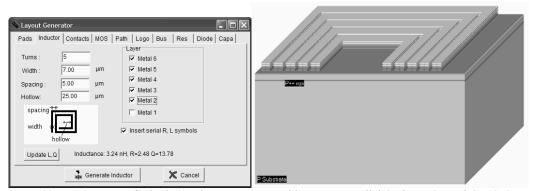

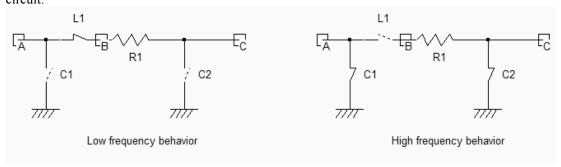

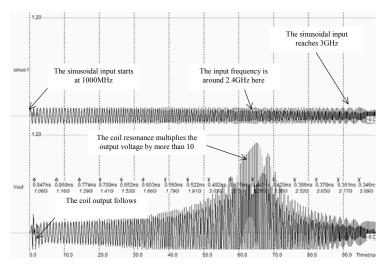

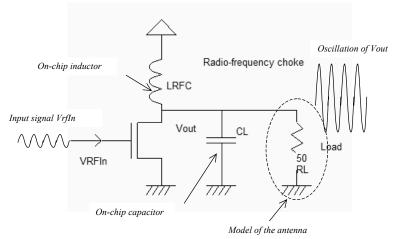

| 10.1         | On-Chip Inductors                                |     |

| 10.1         | Inductor Design in Microwind                     |     |

| 10.2         | <u> </u>                                         |     |

| 10.3         | Power Amplifier<br>Oscillator                    |     |

| 10.4         | Voltage Controlled Oscillator.                   |     |

| 10.5         | Phase-lock-loop                                  |     |

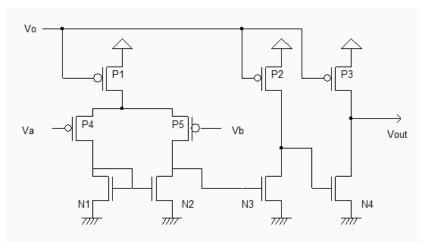

|              | .6.1 Phase Detector                              |     |

|              | .6.2 Filter                                      |     |

|              | .6.3 Voltage controlled oscillator for PLL       |     |

|              | .6.4 Complete Phase Lock Loop                    |     |

| 10.7         | Gilbert Mixer                                    |     |

| 10.8         | Exercises                                        |     |

| 11 (         | Converters                                       | 143 |

| 11.1         | Introduction                                     |     |

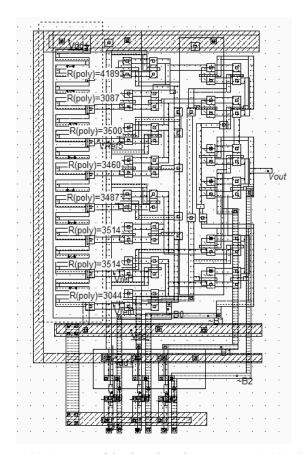

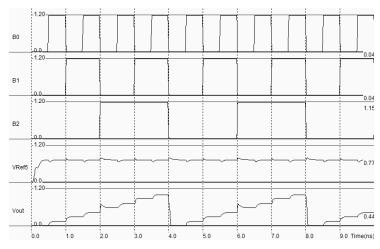

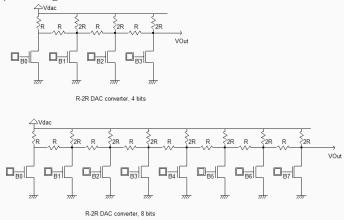

| 11.2         | Digital-Analog Converters architectures          |     |

|              | .2.1 Resistor string converter                   |     |

| 11.          | .2.2 R-2R ladder converter                       |     |

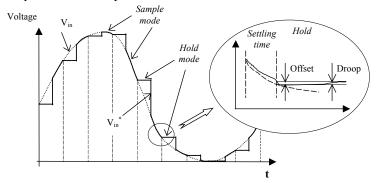

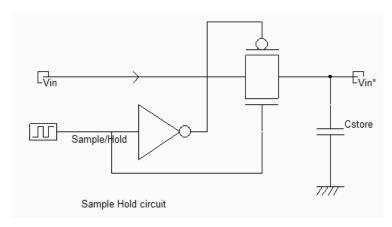

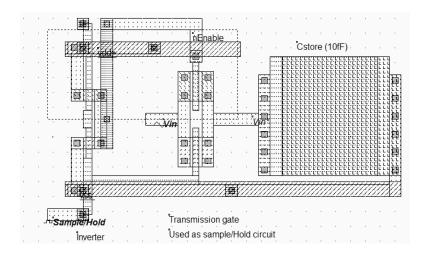

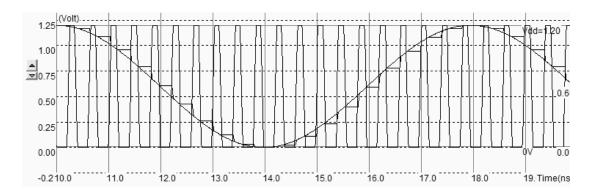

| 11.3         | Sample and Hold circuits                         | 148 |

| 11.4         | Analog-Digital Converters architectures          | 149 |

| 11.          | .4.1 The Flash converter Principles              | 150 |

| 11.4         | .4.2 Low speed ADC Converters                    | 152 |

| 11.5         | Exercises                                        | 153 |

| 12           | Input/Output Interfacing                         | 154 |

| 12.1         | Power Supply                                     | 154 |

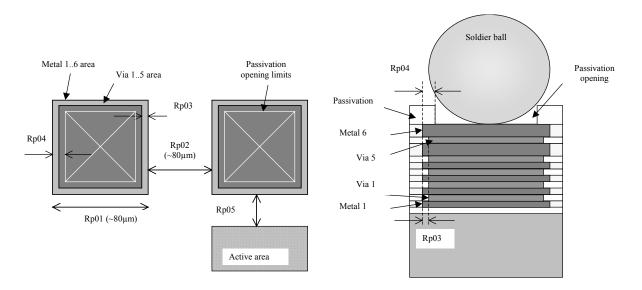

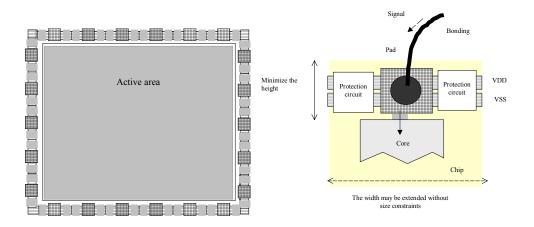

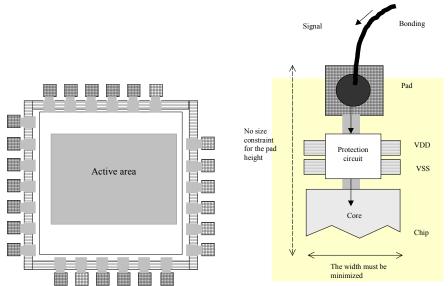

| 12.2         | The Bonding Pad                                  | 155 |

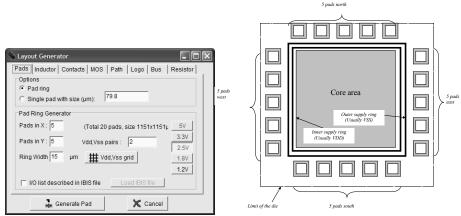

| 12.3         | The Pad ring                                     | 155 |

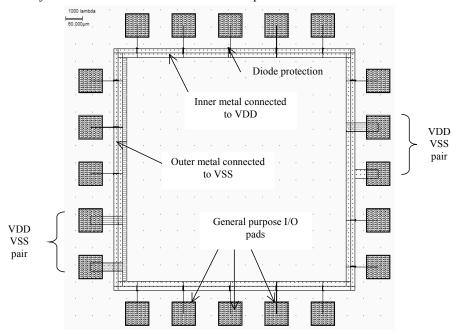

| 12.4         | The supply rails                                 | 156 |

| 12.5         | Input Structures                                 |     |

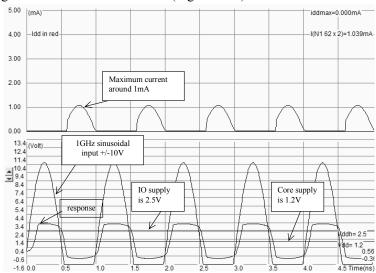

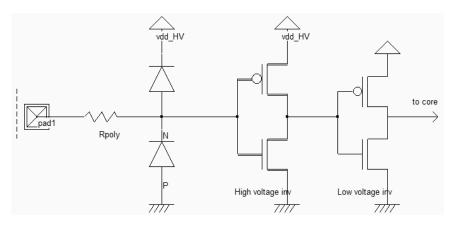

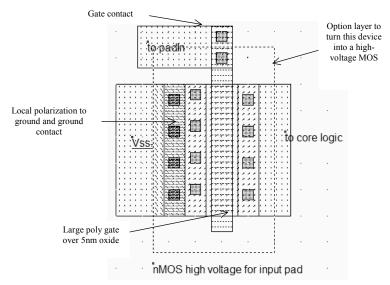

| 12.6         | High voltage MOS                                 | 160 |

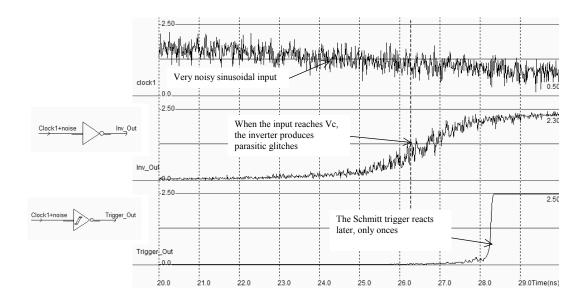

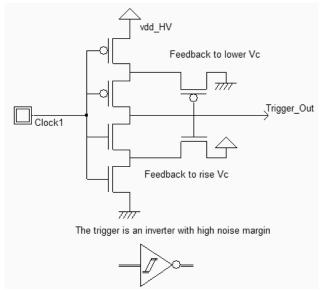

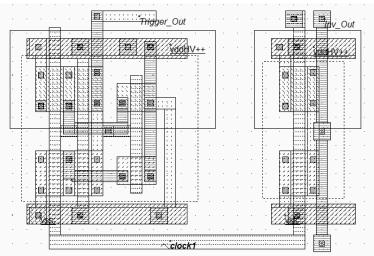

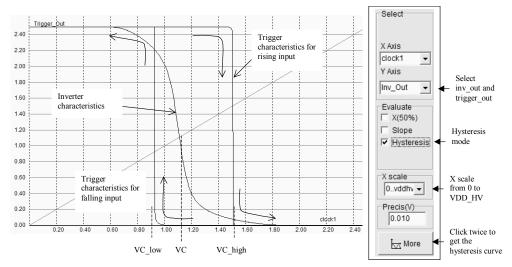

| 12.7         | Input pad with Schmitt Trigger                   |     |

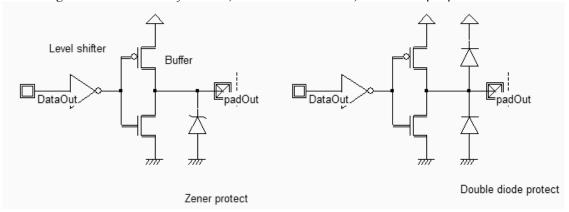

| 12.8         | Digital Output Structures                        | 164 |

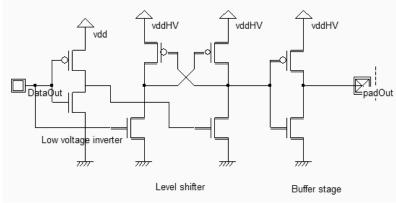

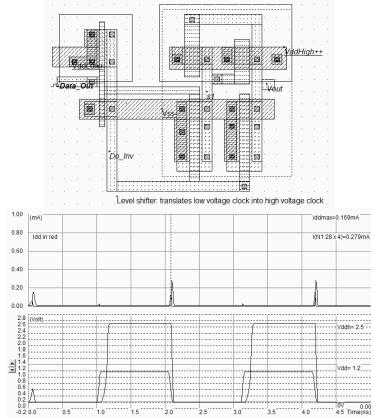

| 12.          | .8.1 Level shifter                               | 165 |

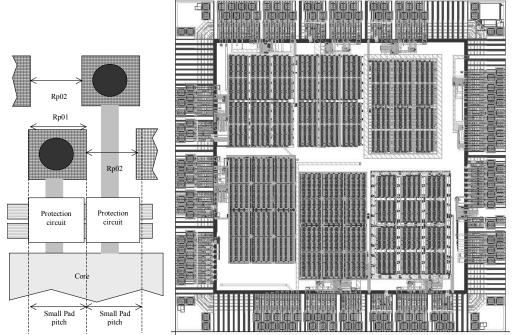

| 12.9         | CORE/PAD LIMITATION                              | 166 |

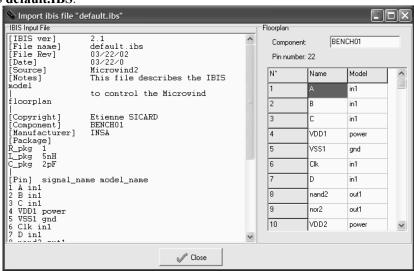

| 12.10        | I/O Pad description using Ibis                   | 168 |

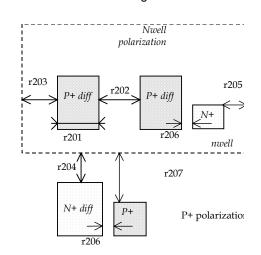

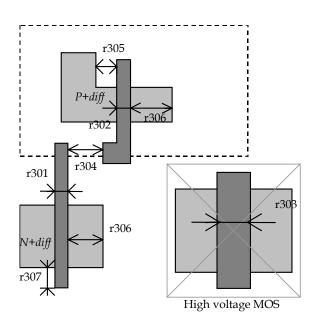

| 13 I         | Design Rules                                     |     |

| 13.1         | Select a Design Rule File                        |     |

| 13.2         | Start Microwind with a specific design Rule File | 170 |

| 13.3         | Lambda Units                                     |     |

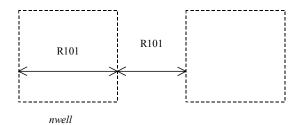

| 13.4         | N-Well                                           | 171 |

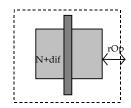

| 13.5         | Diffusion                                        | 171 |

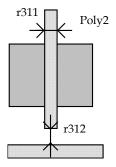

| 13.6         | Polysilicon                                      |     |

| 13.7         | 2 <sup>nd</sup> Polysilicon Design Rules         |     |

| 13.8         | MOS option                                       |     |

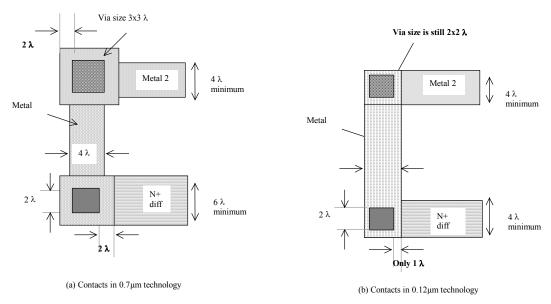

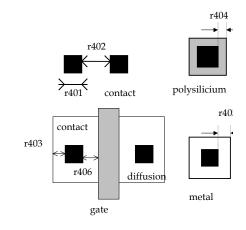

| 13.9         | Contact                                          | 173 |

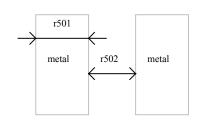

| 13 10        | ) Metal 1                                        | 173 |

#### 1. Introduction

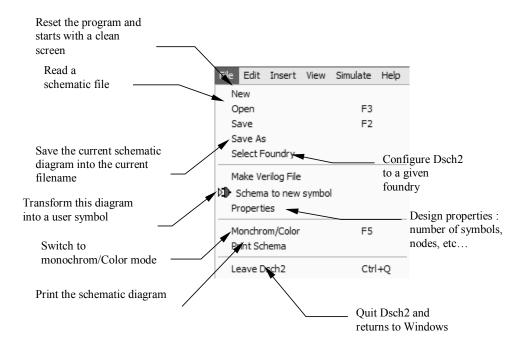

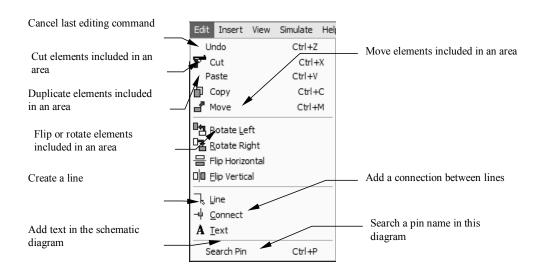

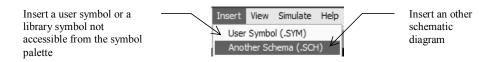

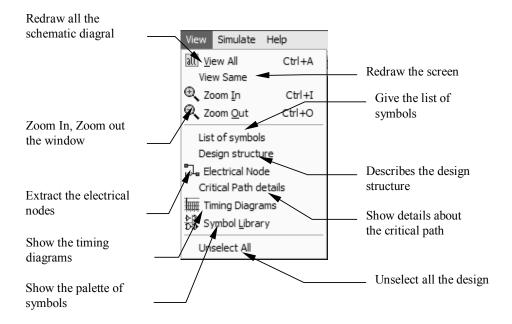

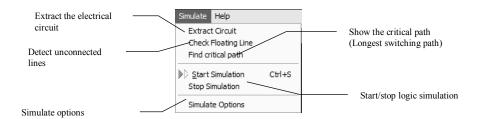

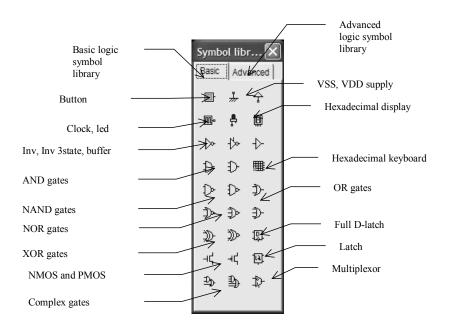

| 14.8<br>14.9<br>14.10<br>14.11<br>14.12<br>14.13<br>14.14<br>14.15<br>14.16<br>14.17<br>14.18<br>14.19 | Microwind2 Simulation menu  Dsch2 Menus  Edit Menu  Insert Menu  View Menu  Simulate Menu  Symbol Palette  List of Files  List of Measurement Files  Measurement file example |                                        |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 14.9<br>14.10<br>14.11<br>14.12<br>14.13<br>14.14<br>14.15<br>14.16<br>14.17<br>14.18                  | Microwind2 Simulation menu  Dsch2 Menus  Edit Menu  Insert Menu  View Menu  Simulate Menu  Symbol Palette  List of Files  List of Measurement Files                           |                                        |

| 14.9<br>14.10<br>14.11<br>14.12<br>14.13<br>14.14<br>14.15<br>14.16<br>14.17                           | Microwind2 Simulation menu Dsch2 Menus Edit Menu Insert Menu View Menu Simulate Menu Symbol Palette List of Files                                                             |                                        |

| 14.9<br>14.10<br>14.11<br>14.12<br>14.13<br>14.14<br>14.15<br>14.16                                    | Microwind2 Simulation menu Dsch2 Menus Edit Menu Insert Menu View Menu Simulate Menu Symbol Palette                                                                           | 188<br>189<br>189<br>189<br>190<br>190 |

| 14.9<br>14.10<br>14.11<br>14.12<br>14.13<br>14.14<br>14.15                                             | Microwind2 Simulation menu Dsch2 Menus Edit Menu Insert Menu View Menu Simulate Menu                                                                                          |                                        |

| 14.9<br>14.10<br>14.11<br>14.12<br>14.13<br>14.14                                                      | Microwind2 Simulation menu Dsch2 Menus Edit Menu Insert Menu View Menu                                                                                                        |                                        |

| 14.9<br>14.10<br>14.11<br>14.12<br>14.13                                                               | Microwind2 Simulation menu Dsch2 Menus Edit Menu Insert Menu                                                                                                                  |                                        |

| 14.9<br>14.10<br>14.11<br>14.12                                                                        | Microwind2 Simulation menu Dsch2 Menus Edit Menu                                                                                                                              |                                        |

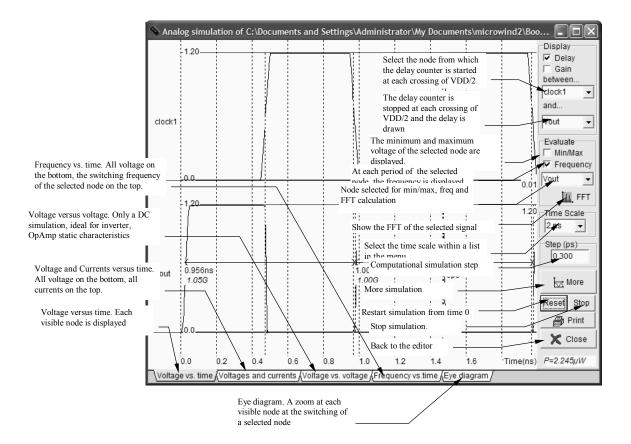

| 14.9<br>14.10<br>14.11                                                                                 | Microwind2 Simulation menu                                                                                                                                                    |                                        |

| 14.9                                                                                                   | Microwind2 Simulation menu                                                                                                                                                    | 188                                    |

|                                                                                                        |                                                                                                                                                                               |                                        |

| 14.8                                                                                                   | LIST OF ICONS                                                                                                                                                                 | 187                                    |

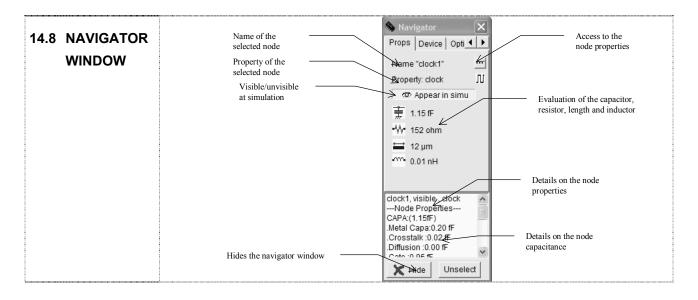

|                                                                                                        | NAVIGATOR WINDOW                                                                                                                                                              |                                        |

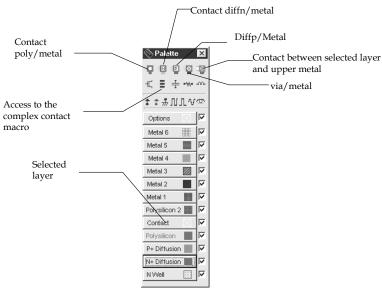

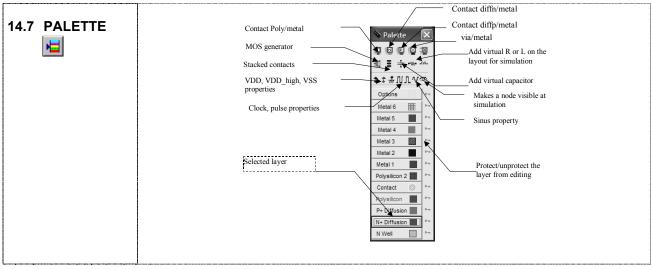

| 14.7                                                                                                   | PALETTE                                                                                                                                                                       | 185                                    |

| 14.6                                                                                                   | ANALYSIS MENU                                                                                                                                                                 |                                        |

| 14.5                                                                                                   | COMPILE MENU                                                                                                                                                                  |                                        |

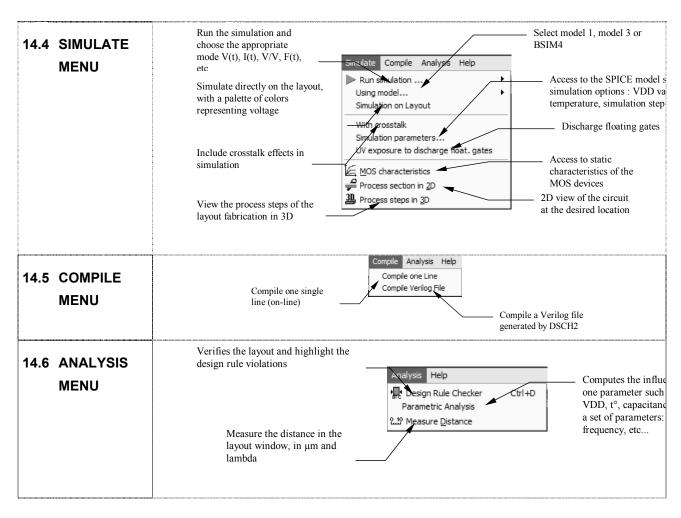

| 14.4                                                                                                   | SIMULATE MENU                                                                                                                                                                 |                                        |

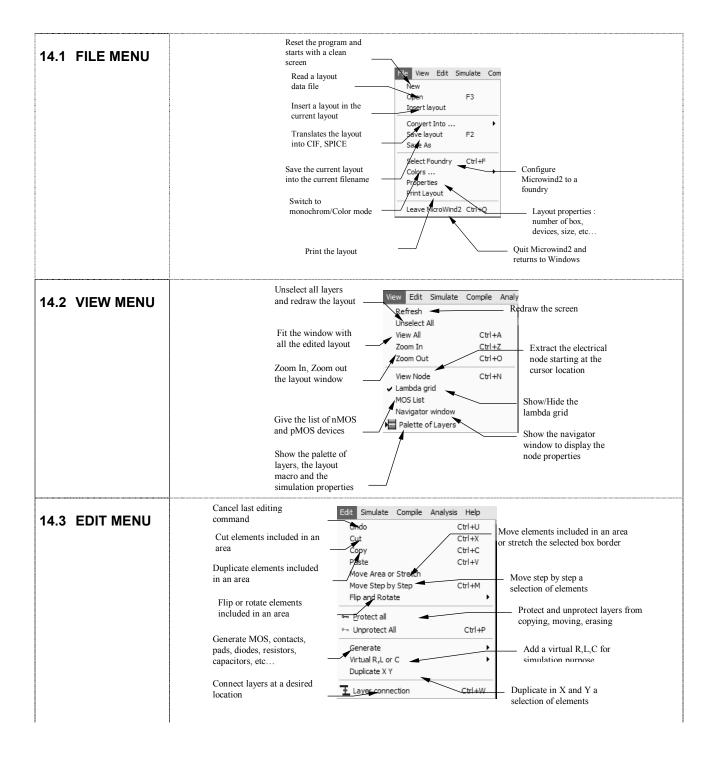

| 14.3                                                                                                   | EDIT MENU                                                                                                                                                                     | 184                                    |

| 14.2                                                                                                   | VIEW MENU                                                                                                                                                                     | 184                                    |

| 14.1                                                                                                   | FILE MENU                                                                                                                                                                     | 184                                    |

| 14 M                                                                                                   | Aicrowind2 Menus                                                                                                                                                              |                                        |

| 13.3⁴                                                                                                  | Design Talle I lie                                                                                                                                                            | 102                                    |

| 13.34                                                                                                  | Design Rule File                                                                                                                                                              |                                        |

| 13.33                                                                                                  | Technology files for DSCH2                                                                                                                                                    |                                        |

| 13.32                                                                                                  | BSIM4 Model for analog simulation                                                                                                                                             |                                        |

| 13.31                                                                                                  | Models Level1 and Level3 for analog simulation                                                                                                                                |                                        |

| 13.29                                                                                                  | Simulation Parameters                                                                                                                                                         |                                        |

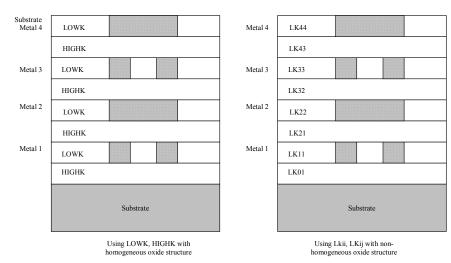

| 13.28                                                                                                  | Dielectrics                                                                                                                                                                   |                                        |

| 13.27                                                                                                  | Resistance Extraction                                                                                                                                                         |                                        |

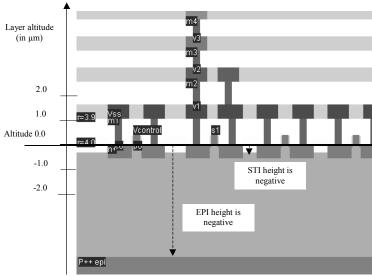

| 13.26                                                                                                  | Parameters for Vertical Aspect of the Technology                                                                                                                              |                                        |

| 13.25<br>13.26                                                                                         | LATERAL CROSSTALK CAPACITANCELATERAL CROSSTALK CAPACITANCE                                                                                                                    |                                        |

| 13.24                                                                                                  | INTER-LAYER CROSSTALK CAPACITANCE                                                                                                                                             |                                        |

| 13.23                                                                                                  | Node Capacitance extraction                                                                                                                                                   |                                        |

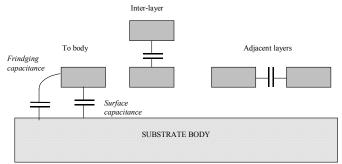

| 13.22                                                                                                  | Electrical Extraction Principles                                                                                                                                              |                                        |

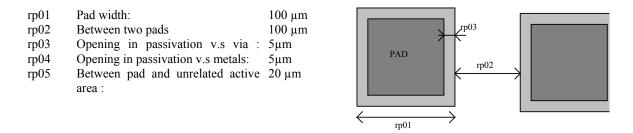

| 13.21                                                                                                  | Pads                                                                                                                                                                          |                                        |

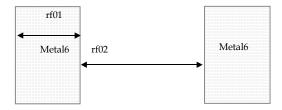

| 13.20                                                                                                  | Metal 6                                                                                                                                                                       |                                        |

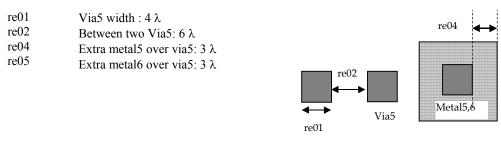

| 13.19                                                                                                  | Via 5                                                                                                                                                                         |                                        |

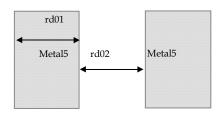

| 13.18                                                                                                  | Metal 5                                                                                                                                                                       |                                        |

| 13.17                                                                                                  | Via 4                                                                                                                                                                         |                                        |

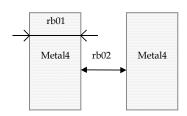

| 13.16                                                                                                  | Metal 4                                                                                                                                                                       |                                        |

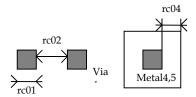

| 13.15                                                                                                  | Via 3                                                                                                                                                                         |                                        |

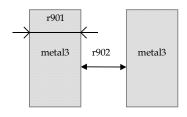

| 13.14                                                                                                  | Metal 3                                                                                                                                                                       |                                        |

| 13.13                                                                                                  | Via 2                                                                                                                                                                         |                                        |

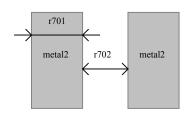

|                                                                                                        | Metal 2                                                                                                                                                                       | 173                                    |

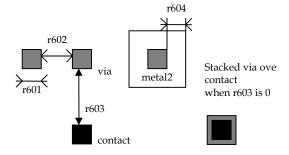

| 13.12                                                                                                  | Via                                                                                                                                                                           | 173                                    |

# 1 Introduction & Installation

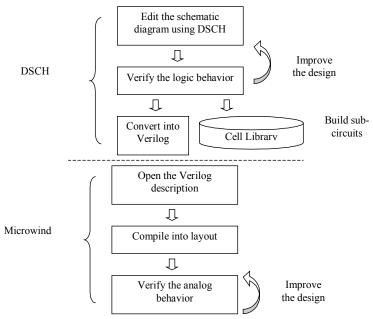

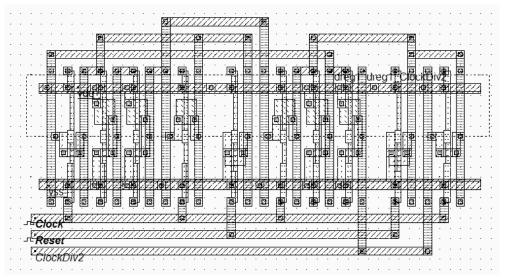

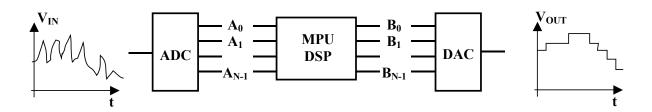

The present manual introduces the design and simulation of CMOS integrated circuits, in an attractive way thanks to user-friendly PC tools Dsch2 and Microwind2.

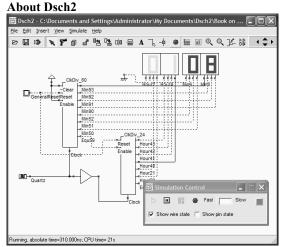

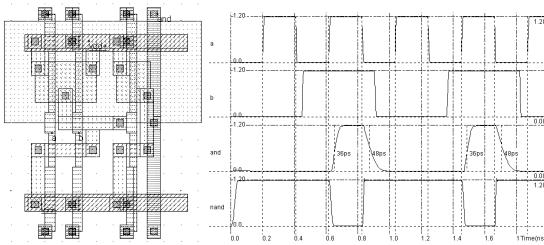

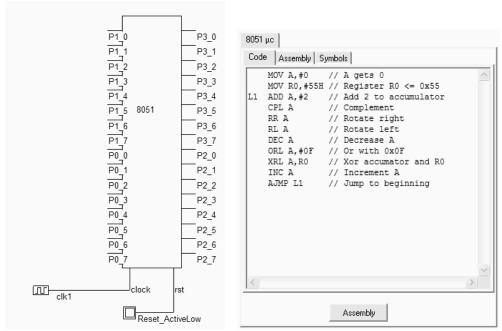

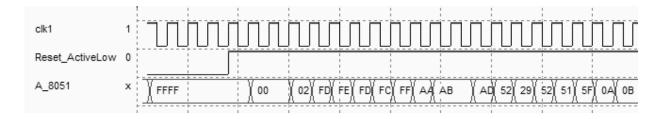

The DSCH2 program is a logic editor and simulator. DSCH2 is used to validate the architecture of the logic circuit before the microelectronics design is started. DSCH2 provides a user-friendly environment for hierarchical logic design, and fast simulation with delay analysis, which allows the design and validation of complex logic structures. Some techniques for low power design are described in the manual. DSCH also features the symbols, models and assembly support for 8051 and 18f64. DSCH also includes an interface to SPICE.

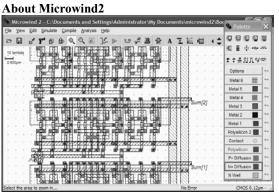

The MICROWIND2 program allows the student to design and simulate an integrated circuit at physical description level. The package contains a library of common logic and analog ICs to view and simulate. MICROWIND2 includes all the commands for a mask editor as well as original tools never gathered before in a single module (2D and 3D process view, VERILOG compiler, tutorial on MOS devices). You can gain access to *Circuit Simulation* by pressing one single key. The electric extraction of your circuit is automatically performed and the analog simulator produces voltage and current curves immediately.

The chapters of this manual have been summarized below. Chapter 2 describes the technology scale down and the major improvements given by deep sub-micron technologies. Chapter 3 is dedicated to the presentation of the single MOS device, with details on the device modeling, simulation at logic and layout levels. Chapter 4 presents the CMOS Inverter, the 2D and 3D views, the comparative design in micron and deep-submicron technologies. Chapter 5 concerns the basic logic gates (AND, OR, XOR, complex gates), Chapter 6 the arithmetic functions (Adder, comparator, multiplier, ALU). The latches and memories are detailed in Chapter 7.

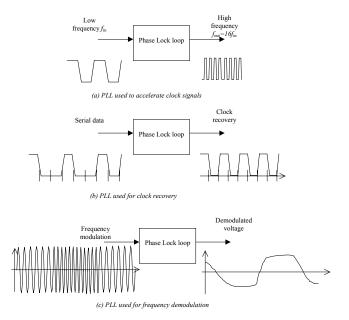

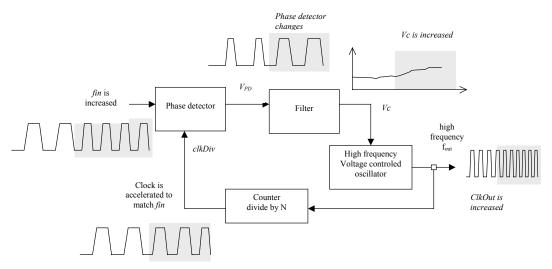

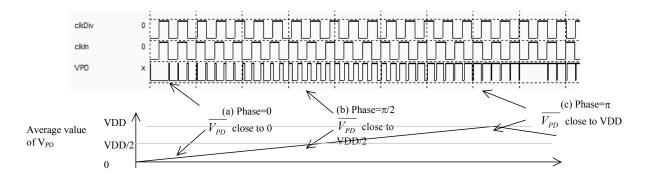

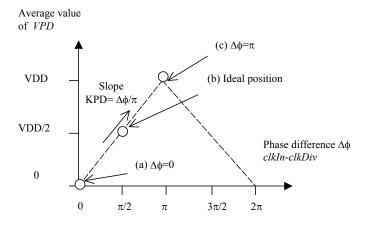

As for Chapter 8, analog cells are presented, including voltage references, current mirrors, operational amplifiers and phase lock loops. Chapter 9 concerns analog-to-digital and digital to analog converter principles. Chapter 10 is dedicated to radio-frequency circuit. The input/output interfacing principles are illustrated in Chapter 11.

The detailed explanation of the design rules is in Chapter 12. Electrical rules are described in chapter 13. The program operation and the details of all commands are given in the help files of the programs.

#### **INSTALLATION**

#### From The web

Connect to page http://www.microwind.org

Click "Introduction to microelectronics"

- ◆ Click "Download MICROWIND2 (ZIP file)". In your PC, create manually a directory (Suggested : c:\program files\microwind2). Store the ZIP file in this directory.

- Extract all files in the selected directory

- ◆ Test: double-click MICROWIND2.EXE. Click "File ->Load", select "CMOS.msk". Click "Simulate".

- ◆ Click "Download DSCH2 (ZIP file)". In your PC, create manually a directory (Suggested : c:\program files\dsch2). Store the ZIP file in this directory.

- Extract all files in the selected directory.

- ♦ Test: double click in DSCH2.EXE. Load "base.sch". Click "Simulate".

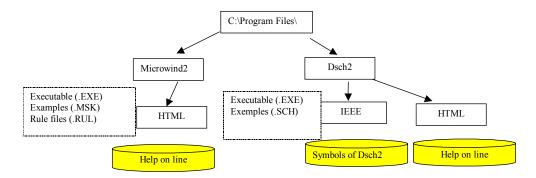

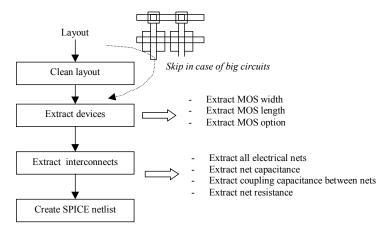

Figure 1: The architecture of Microwind and Dsch

Once installed, two directories are created, one for Microwind, one for Dsch. In each directory, a subdirectory called html contains help files.

# 2 Technology Scale Down

The evolution of integrated circuit (IC) fabrication techniques is a unique fact in the history of modern industry. The improvements in terms of speed, density and cost have keep constant for more than 30 years. By the end of 2004, "System-on-Chips" with about 300,000,000 transistors will be fabricated on a single piece of silicon no larger than 2x2 cm. In this chapter, we present some information illustrating the technology scale down.

#### 2.1 Evolution of Microprocessors and Memories

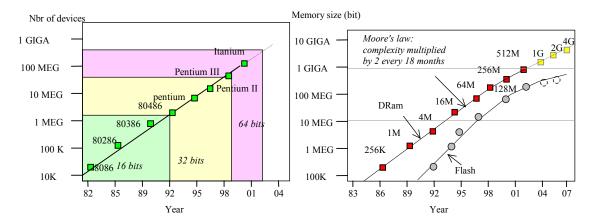

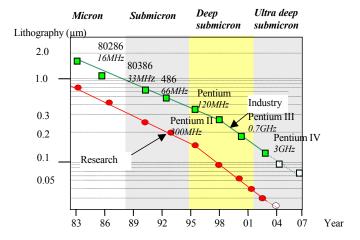

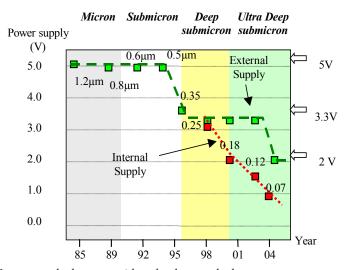

Figure 2-1 describes the evolution of Intel ® microprocessors, figure 2-2 describes the evolution of memory size during the last decades. In figure 3, it is shown that industry has started to produce ICs in deep submicron technology starting 1995. Research has always kept around 5 years ahead mass production.

Fig. 2-1: Evolution of microprocessors

Fig.2-2: Evolution of memories

Fig. 2-3: Evolution of lithography

#### 2.2 Frequency Improvements

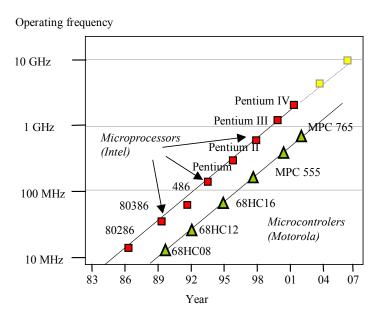

Fig. 2-4: Reduced device features and increased interconnect layers

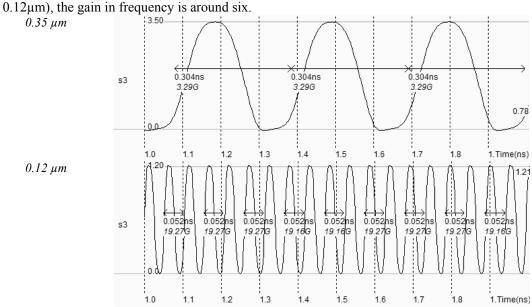

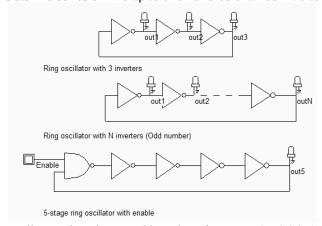

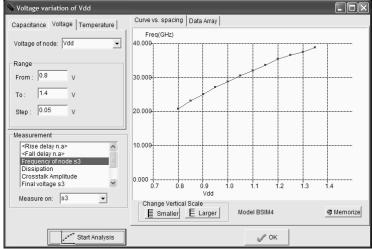

Figure 2-4 illustrates the main improvements in terms of clock frequency for Intel microprocessors and Motorola micro-controllers. An illustration of this trend towards higher frequencies is given below (Figure 5), with a ring oscillator made from 3 inverters, simulated with MICROWIND2 using  $0.35\mu m$  and  $0.12\mu m$  technologies. Although the supply voltage has been cut by more than half (VDD is 3.3V in  $0.35\mu m$ , 1.2 in  $0.12\mu m$ ), the gain in frequency is around six

Fig. 2-5: Improvement in speed thanks to deep submicron technology

#### **HOW TO SIMULATE**

- ① Start Microwind2. By default the software is configured with  $0.12\mu m$  technology. Click **File**  $\rightarrow$  **Open**.

- ② Select INV3. Click **Simulate→ Start Simulation**. The oscillation on the bottom of figure 2-5 appears.

- 3 Click Close.

- ④ Click File → Select Foundry. Click cmos35.rul.

- ⑤ Run again the simulation. Observe the change of VDD and the slow down of the oscillating frequency.

#### 2.3 Increased Layers

The table below lists a set of key parameters, and their evolution with the technology. Worth of interest is the increased number of metal interconnects the reduction of the power supply VDD and the reduction of the gate oxide down to atomic scale values. Notice also the slow decrease of the threshold voltage of the MOS device and the increasing number of input/output pads available on a single die.

| Lithography | Year | Metal  | Core   | Core Oxide | Chip size | Input/output | Microwind2  |

|-------------|------|--------|--------|------------|-----------|--------------|-------------|

|             |      | layers | supply | (nm)       | (mm)      | pads         | rule file   |

|             |      |        | (V)    |            |           |              |             |

| 1.2µm       | 1986 | 2      | 5.0    | 25         | 5x5       | 250          | Cmos12.rul  |

| 0.7µm       | 1988 | 2      | 5.0    | 20         | 7x7       | 350          | Cmos08.rul  |

| 0.5µm       | 1992 | 3      | 3.3    | 12         | 10x10     | 600          | Cmos06.rul  |

| 0.35µm      | 1994 | 5      | 3.3    | 7          | 15x15     | 800          | Cmos035.rul |

| 0.25µm      | 1996 | 6      | 2.5    | 5          | 17x17     | 1000         | Cmos025.rul |

| 0.18µm      | 1998 | 6      | 1.8    | 3          | 20x20     | 1500         | Cmos018.rul |

| 0.12µm      | 2001 | 6-8    | 1.2    | 2          | 22x20     | 1800         | Cmos012.rul |

| 90nm        | 2003 | 6-10   | 1.0    | 1.8        | 25x20     | 2000         | Cmos90n.rul |

| 65nm        | 2005 | 6-12   | 0.8    | 1.6        | 25x20     | 3000         | Cmos70n.rul |

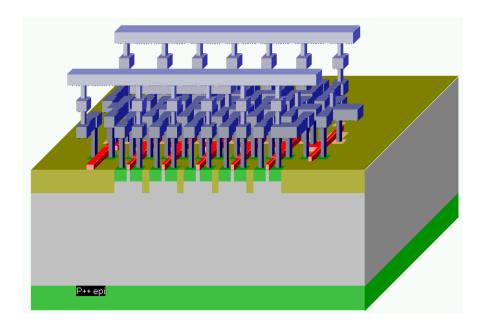

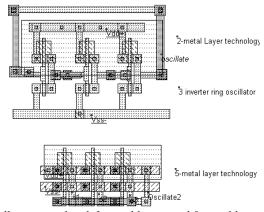

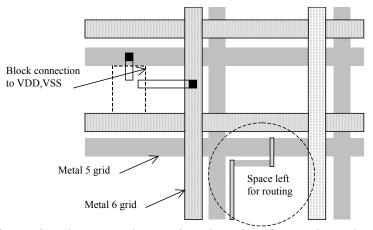

Fig. 2-6: A three-inverter ring oscillator routed with 2-metal layers and 5-metal layers technologies

As can be noticed, the number of metal layers used for interconnects has been continuously increasing in the course of the past ten years. More layers for routing means a more efficient use of the silicon surface, as for printed circuit boards. Active areas, i.e MOS devices can be placed closer from each other if many routing layers are provided (Figure 2-6).

#### **HOW TO SIMULATE**

- ① Start Microwind2. By default the software is configured with  $0.12\mu m$  technology. Click **File**  $\rightarrow$ **Open**.

- ② Select INV3. Click Simulate→ Process section in 2D.

- ③ Draw a line representing the location for 2D-process view. The 2D view appears. Click **OK**.

- ④ Click Simulate → Start Simulation. Observe the oscillator frequency.

- ⑤ Click File →Select Foundry. Change the technology (For example cmos035.rul)

- © Ask again for the 2D view. Observe the change in the process aspect.

- ② Ask again for analog simulation. Observe the change in frequency and voltage supply.

#### 2.4 Design Trends

Originally, integrated circuits were designed at layout level, with the help of logic design tools, to achieve design complexities of around 10,000 transistors. The Microwind layout tool works at the lowest level of design, while DSCH operates at logic level.

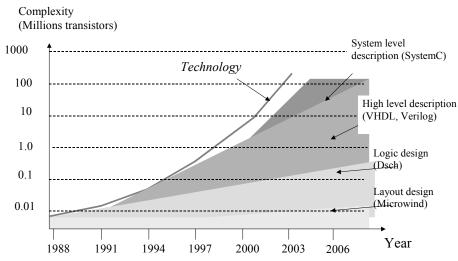

Figure 2-7: The evolution of integrated circuit design techniques, from layout level to system level

#### 2.5 Exercises

- 1. Plot the frequency improvement versus the technology for the CMOSxx technology family, using the 3-inverter ring oscillator. Can you guess the performances of the 35nm technology?

- 2. Does the 3-inverter frequency performance represent the microprocessor frequency correctly? Use date of figure 1-3 to build your answer.

- 3. From the 2D comparative aspect of  $0.35\mu m$  and  $0.12\mu m$  technologies, what may be the rising problems of using multiple metallization layers?

# 3 The MOS device

This chapter presents the CMOS transistor, its layout, static characteristics and dynamic characteristics. The vertical aspect of the device and the three dimensional sketch of the fabrication are also described.

#### 3.1 Logic Levels

Three logic levels 0,1 and X are defined as follows:

| Logical value | Voltage                | Name | Symbol in DSCH              | Symbol in Microwind          |

|---------------|------------------------|------|-----------------------------|------------------------------|

| 0             | 0.0V                   | VSS  | (Green in logic simulation) | (Green in analog simulation) |

| 1             | 1.2V in cmos<br>0.12μm | VDD  | (Red in logic simulation)   | (Red in analog simulation)   |

| X             | Undefined              | X    | (Gray in simulation)        | (Gray in simulation)         |

#### 3.2 The MOS as a switch

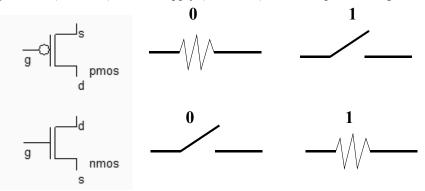

The MOS transistor is basically a switch. When used in logic cell design, it can be *on* or *off*. When *on*, a current can flow between drain and source. When off, no current flow between drain and source. The MOS is turned on or off depending on the gate voltage. In CMOS technology, both n-channel (or nMOS) and p-channel MOS (or pMOS) devices exist. The nMOS and pMOS symbols are reported below. The symbols for the ground voltage source (0 or VSS) and the supply (1 or VDD) are also reported in figure 3-1.

Fig. 3-1: the MOS symbol and switch

The n-channel MOS device requires a logic value 1 (or a supply VDD) to be on. In contrary, the p-channel MOS device requires a logic value 0 to be on. When the MSO device is on, the link between the source and

13/12/03

drain is equivalent to a resistance. The order of range of this 'on' resistance is  $100\Omega$ -5K $\Omega$ . The 'off' resistance is considered infinite at first order, as its value is several M $\Omega$ .

#### 3.3 Logic Simulation of the MOS

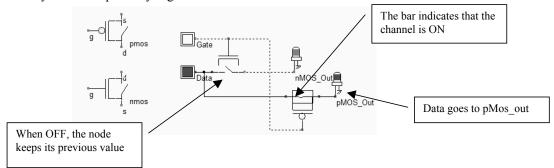

At logic level, the MOS is considered as a simple switch. Moreover, the logic switch is unidirectional, meaning that the logic signal always flows from the source to the drain. This major restriction has no physical background. In reality, the current may flow both ways. The reason why the logic MOS device enables the signal to propagate only from source to drain is purely a software implementation problem. In the logic simulator of DSCH2, an arrow indicates whether or not the current flows, and its direction (Figure 3.2). When the device is OFF, the drain keeps its last logic value, thus acting as an elementary memory. Notice that you cannot pass any logic information from the drain to the source. Such a circuit would fail.

Fig. 3-2: the logic simulation of the MOS device (MosExplain.SCH)

#### 3.4 MOS layout

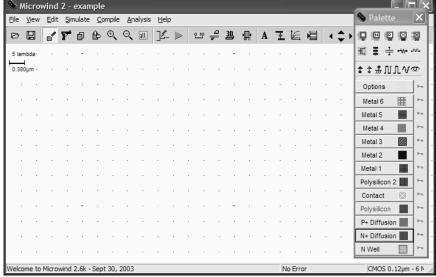

We use MICROWIND2 to draw the MOS layout and simulate its behavior. Go to the directory in which the software has been copied (By default microwind2). Double-click on the MicroWind2 icon.

The MICROWIND2 display window includes four main windows: the main menu, the layout display window, the icon menu and the layer palette. The layout window features a grid, scaled in lambda ( $\lambda$ ) units. The lambda unit is fixed to half of the minimum available lithography of the technology. The default technology is a CMOS 6-metal layers 0.12 $\mu$ m technology, consequently lambda is 0.06 $\mu$ m (60nm).

Fig. 3-3 The MICROWIND2 window as it appears at the initialization stage...

The palette is located in the lower right corner of the screen. A red color indicates the current layer. Initially the selected layer in the palette is polysilicon. By using the following procedure, you can create a manual design of the n-channel MOS.

- Fix the first corner of the box with the mouse. While keeping the mouse button pressed, move the mouse to the opposite corner of the box. Release the button. This creates a box in polysilicon layer as shown in Figure 3-4. The box width should not be inferior to  $2 \lambda$ , which is the minimum width of the polysilicon box.

- Change the current layer into N+ diffusion by a click on the palette of the Diffusion N+ button. Make sure that the red layer is now the N+ Diffusion. Draw a n-diffusion box at the bottom of the drawing as in Figure 3-4. N-diffusion boxes are represented in green. The intersection between diffusion and polysilicon creates the channel of the nMOS device.

Fig. 3-4. Creating the N-channel MOS transistor

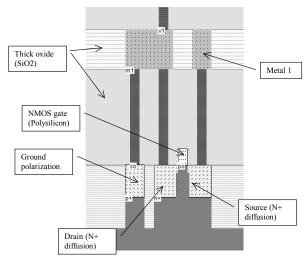

#### 3.5 Vertical aspect of the MOS

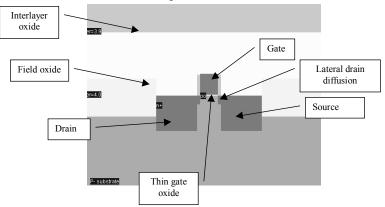

Click on this icon to access *process simulation* (Command *Simulate*  $\rightarrow$  *Process section in 2D*). The cross-section is given by a click of the mouse at the first point and the release of the mouse at the second point.

Fig. 3-5. The cross-section of the nMOS devices.

In the example of Figure 3-5, three nodes appear in the cross-section of the n-channel MOS device: the gate (red), the left diffusion called *source* (green) and the right diffusion called *drain* (green), over a substrate (gray). A thin oxide called the gate oxide isolates the gate. Various steps of oxidation have lead to stacked oxides on the top of the gate.

The physical properties of the source and of the drain are exactly the same. Theoretically, the source is the origin of channel impurities. In the case of this nMOS device, the channel impurities are the electrons. Therefore, the source is the diffusion area with the lowest voltage. The polysilicon gate floats over the channel, and splits the diffusion into 2 zones, the source and the drain. The gate controls the current flow from the drain to the source, both ways. A high voltage on the gate attracts electrons below the gate, creates an electron channel and enables current to flow. A low voltage disables the channel.

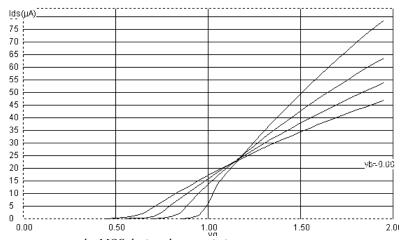

#### 3.6 Static Mos Characteristics

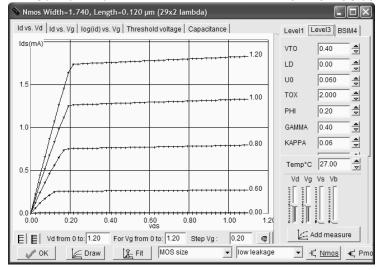

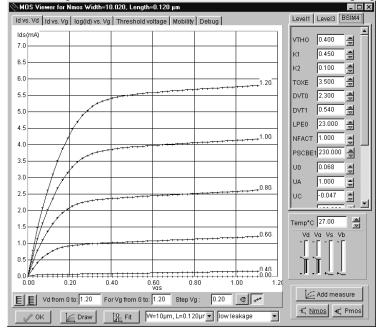

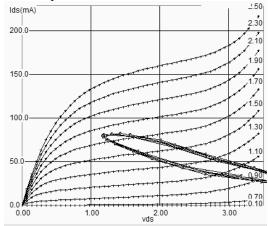

Click on the *MOS characteristics* icon. The screen shown in Figure 2-6 appears. It represents the *Id/Vd* static characteristics of the nMOS device.

Fig. 3-6. N-Channel MOS characteristics.

The MOS size (width and length of the channel situated at the intersection of the polysilicon gate and the diffusion) has a strong influence on the value of the current. In Figure 3-6, the MOS width is  $1.74\mu m$  and the length is  $0.12\mu m$ . A high gate voltage (Vg = 1.2V) corresponds to the highest Id/Vd curve. For Vg = 0, no current flows. You may change the voltage values of Vd, Vg, Vs by using the voltage cursors situated on the right side of the window. A maximum current around 1.5mA is obtained for Vg = 1.2V, Vd = 1.2V, with Vs = 0.0. The MOS parameters correspond to SPICE Level 3. A tutorial on MOS model parameters is proposed later in this chapter.

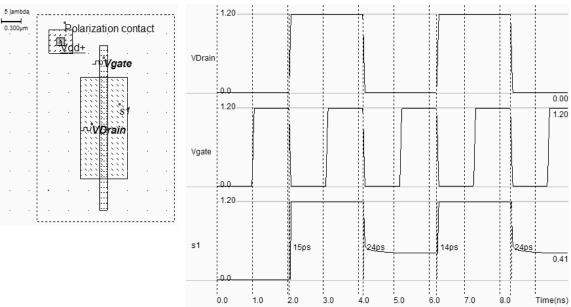

#### 3.7 Dynamic MOS behavior

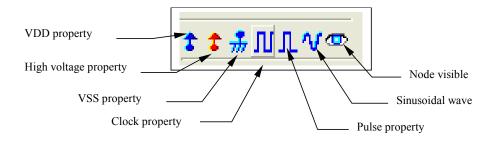

This paragraph concerns the dynamic simulation of the MOS to exhibit its switching properties. The most convenient way to operate the MOS is to apply a clock to the gate, another to the source and to observe the drain. The summary of available properties that can be added to the layout is reported below.

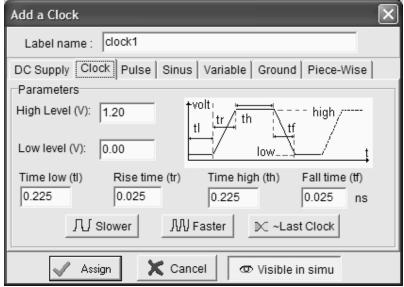

• Apply a clock to the gate. Click on the *Clock* icon and then, click on the polysilicon gate. The clock menu appears again. Change the name into Vgate and click on **OK** to apply a clock with 0.5ns period (0.225ns at 0, 25ps rise, 0.225ns at 1, 25ps fall).

Fig. 3-7. The clock menu.

- Apply a clock to the drain. Click on the Clock icon, click on the left diffusion. The *Clock* menu appears. Change the name into Vdrain and click on **OK**. A default clock with 1ns period is generated. The *Clock* property is sent to the node and appears at the right hand side of the desired location with the name Vdrain.

- Watch the output: Click on the *Visible* icon and then, click on the right diffusion. Click **OK**. The Visible property is then sent to the node. The associated text s1 is in italic, meaning that the waveform of this node will appear at the next simulation.

Always save <u>BEFORE</u> any simulation. The analog simulation algorithm may cause run-time errors leading to a loss of layout information. Click on **File**  $\rightarrow$  **Save as**. A new window appears, into which you enter the design name. Type for example myMos. Then click on **Save**. The design is saved under that filename.

#### 3.8 Analog Simulation

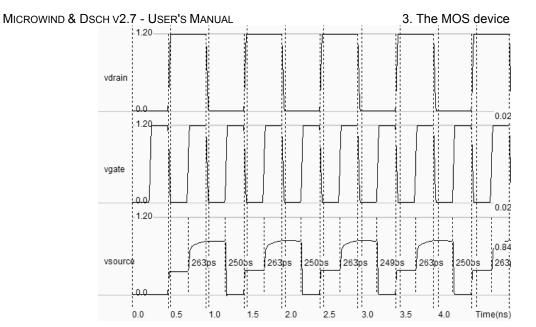

Click on **Simulate** → **Start Simulation**. The timing diagrams of the nMOS device appear, as shown in Figure 3-8.

Fig. 3-8. Analog simulation of the MOS device.

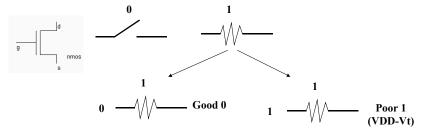

When the gate is at zero, no channel exists so the node *vsource* is disconnected from the drain. When the gate is on, the source copies the drain. It can be observed that the nMOS device drives well at zero but poorly at the high voltage. The highest value of *vsource* is around 0.85V, that is VDD minus the threshold voltage. This means that the n-channel MOS device do not drives well logic signal 1, as summarized in figure 3-9. Click on **More** in order to perform more simulations. Click on **Close** to return to the editor.

Fig. 3-9. The nMOS device behavior summary

#### 3.9 Layout considerations

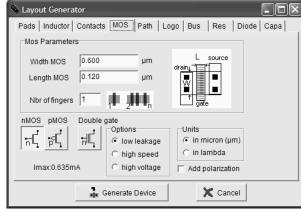

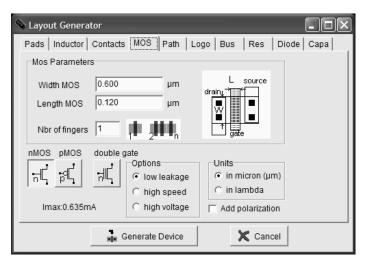

The safest way to create a MOS device is to use the MOS generator. In the palette, click the MOS generator icon. A window appears as reported below. The programmable parameters are the MOS width, length, the number of gates in parallel and the type of device (n-channel or p-channel). By default metal interconnects and contacts are added to the drain and source of the MOS. You may add a supplementary metal2 interconnect on the top of metal 1 for drain and source.

#### MICROWIND & DSCH V2.7 - USER'S MANUAL

# 3. The MOS device

Fig. 3-10. The MOS generator

#### 3.10 The MOS Model 1

For the evaluation of the current *Ids* between the drain and the source as a function of *Vd*, *Vg* and *Vs*, you may use the old but nevertheless simple MODEL 1 described below.

| Mode      | Condition                                                                                                                                             | Expression for the current <i>Ids</i>                                                |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| CUT-OFF   | Vgs<0                                                                                                                                                 | Ids = 0                                                                              |

| LINEAR    | Vds <vgs-vt< td=""><td><math display="block">Ids = UO \frac{\varepsilon_0 \varepsilon_r}{TOX} \cdot \frac{W}{L} (V_{gs} - vt)^2</math></td></vgs-vt<> | $Ids = UO \frac{\varepsilon_0 \varepsilon_r}{TOX} \cdot \frac{W}{L} (V_{gs} - vt)^2$ |

| SATURATED | Vds>Vgs-Vt                                                                                                                                            | $Ids = UO \frac{\varepsilon_0 \varepsilon_r}{TOX} \cdot \frac{W}{L} (V_{gs} - vt)^2$ |

With:

$$vt = VTO + GAMMA(\sqrt{(PHI - vb)} - \sqrt{PHI})$$

$\varepsilon_0 = 8.85 \, 10^{-12} \, \text{F/m}$  is the absolute permittivity

$\varepsilon_r$  = relative permittivity, equal to 3.9 in the case of SiO2 (no unit)

| Mos Model 1 parameters |                                       |                              |                              |  |  |

|------------------------|---------------------------------------|------------------------------|------------------------------|--|--|

| Parameter              | Definition                            | Typical Value 0.12µm         |                              |  |  |

|                        |                                       | NMOS                         | PMOS                         |  |  |

| VTO                    | Theshold voltage                      | 0.4V                         | -0.4V                        |  |  |

| U0                     | Carrier mobility                      | $0.06 \text{m}^2/\text{V-s}$ | $0.02 \text{m}^2/\text{V-s}$ |  |  |

| TOX                    | Gate oxide thickness                  | 2nm                          | 2nm                          |  |  |

| PHI                    | Surface potential at strong inversion | 0.3V                         | 0.3V                         |  |  |

| GAMMA                  | Bulk threshold parameter              | $0.4 \text{ V}^{0.5}$        | $0.4 \text{ V}^{0.5}$        |  |  |

| W MOS channel width    |                                       | 1μm                          | 1μm                          |  |  |

| L MOS channel length   |                                       | 0.12µm                       | 0.12µm                       |  |  |

Table 3-1: Parameters of MOS level 1 implemented into Microwind2

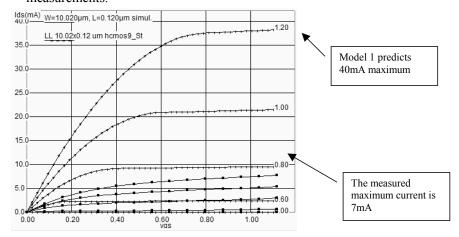

Let us compare the simulation and the measurement, for a 10x10µm device.

- Click Simulate → Mos characteristics (Or the icon

- **2** Click **Add Measure**.

- Select the data file Ne10x0,12.MES. The "N" means an n-channel MOS device. The "e" corresponds to a test chip fabricated in 0.12μm technology. The values 10x0,12 means Width=10μm, Length=0.12μm.

- Select "Level 1" in the parameter list to compare LEVEL1 simulated characteristics with the measurements.

Fig. 3-11: The model 1 predict a current 4 times higher than the measurement

When dealing with sub-micron technology, the model 1 is more than 4 times too optimistic regarding current prediction, compared to real-case measurements, as shown above for a  $10x0,12\mu m$  n-channel MOS.

#### 3.11 The MOS Model 3

For the evaluation of the current Ids as a function of Vd, Vg and Vs between drain and source, we commonly use the following equations, close from the SPICE model 3 formulations. The formulations are derived from the model 1 and take into account a set of physical limitations in a semi-empirical way.

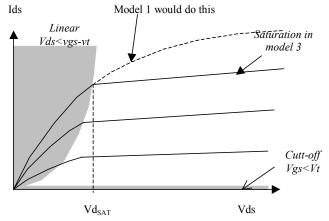

Fig. 3-12: Introduction of the saturation voltage VdSat which truncates the equations issued from model 1

One of the most important change is the introduction of  $Vd_{SAT}$ , a saturation voltage from which the current saturates and do not rise as the LEVEL1 model would do (Figure 3-12). This saturation effect is significant for small channel length. The main LEVEL3 equations are listed below.

NORMAL MODE. Vgs>Von

$$Ids = Keff \frac{W}{Leff} (1 + KAPPA.Vds)Vde((Vgs - Vth) - \frac{Vde}{2})$$

with

$$Von = 1.2Vth$$

$$Vth = \text{VTO} + \text{GAMMA}(\sqrt{\text{PHI}} - Vbs) - \sqrt{\text{PHI}})$$

$$Vde = min(Vds, Vdsat)$$

$$Vdsat = Vc + Vsat - \sqrt{Vc^2 + Vsat^2}$$

$$Vdsat = Vgs - Vth$$

$$Vc = \text{VMAX} \frac{Leff}{0.06}$$

$$Leff = L - 2LD$$

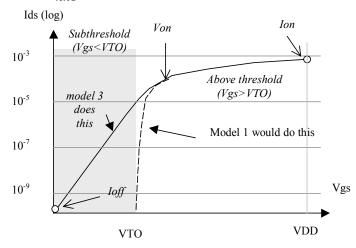

The sub-threshold mode corresponds to Vgs < VTO. The model 3 includes a specific set of equations based on an exponential decrease of Ids, as compared to Ids = 0 predicted by model 1.

$$Ids = Ids(Von, Vds)exp(\frac{q(Vgs - Von)}{nkT})$$

Figure 3-13: Introduction of an exponential law to model the sub-threshold behavior of the current

| Parameter | Definition | Typical Value 0.12μm |

|-----------|------------|----------------------|

|           |            | NMOS pMOS            |

| _   | <b>T</b> 1 | 1100  |      |     |

|-----|------------|-------|------|-----|

| ٠.٧ | ınΔ        | MOS   | MAN/ | 100 |

| J.  | 1110       | IVICO | ucv  |     |

| VTO   | The shold voltage of a long channel   | 0.4V                          | -0.4V                          |

|-------|---------------------------------------|-------------------------------|--------------------------------|

|       | device, at zero Vbs.                  |                               |                                |

| U0    | Carrier mobility                      | $0.06 \text{ m}^2/\text{V.s}$ | $0.025 \text{ m}^2/\text{V.s}$ |

| TOX   | Gate oxide thickness                  | 3 nm                          | 3 nm                           |

| PHI   | Surface potential at strong inversion | 0.3V                          | 0.3V                           |

| LD    | Lateral diffusion into channel        | 0.01µm                        | 0.01µm                         |

| GAMMA | Bulk threshold parameter              | $0.4 \text{ V}^{0.5}$         | $0.4 \text{ V}^{0.5}$          |

| KAPPA | Saturation field factor               | 0.01 V <sup>-1</sup>          | 0.01 V <sup>-1</sup>           |

| VMAX  | Maximum drift velocity                | 150Km/s                       | 100Km/s                        |

| THETA | Mobility degradation factor           | 0.3 V <sup>-1</sup>           | 0.3 V <sup>-1</sup>            |

| NSS   | Substhreshold factor                  | 0.07 V <sup>-1</sup>          | 0.07 V <sup>-1</sup>           |

| W     | MOS channel width                     | 0.5-20µm                      | 0.5-40µm                       |

| L     | MOS channel length                    | 0.12µm                        | 0.12μm                         |

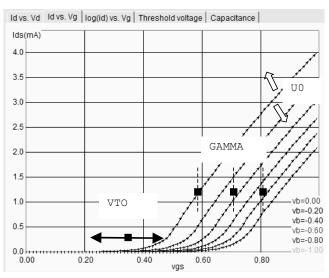

The curve shown in Figure 3-14 shows the effects of VTO, U0 and GAMMA. Act on VTO cursors in order to shift the curves right or left, U0 to adjust the slope, and GAMMA to fit the spacing between curves.

Fig. 3-14. Effect of KP, VTO and GAMMA on the Id/Vd curve

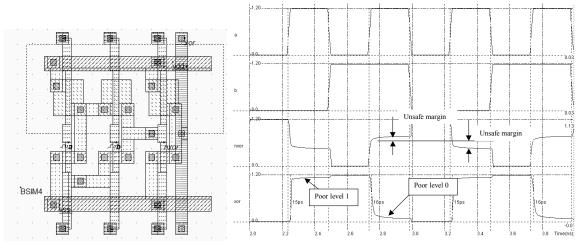

#### 3.12 The BSIM4 MOS Model

A family of models has been developed at the University of Berkeley for the accurate simulation of submicron technology. The Berkeley Short-channel IGFET Model (BSIM) exist in several version (BSIM1, BSIM2, BSIM3). The BSIM3v3 version, promoted by the Electronic Industries Alliance (EIA) is an industry standard for deep-submicron device simulation.

A new MOS model, called BSIM4, has been introduced in 2000. A simplified version of this model is supported by Microwind2, and recommended for ultra-deep submicron technology simulation. BSIM4 still considers the operating regions described in MOS level 3 (linear for low Vds, saturated for high Vds, subthreshold for Vgs < Vt), but provides a perfect continuity between these regions. BSIM4 introduces a new region where the impact ionization effect is dominant.

The number of parameters specified in the official release of BSIM4 is as high as 300. A significant portion of these parameters is unused in our implementation. We concentrate on the most significant parameters, for educational purpose. The set of parameters is reduced to around 20, shown in the right part of figure 3-15.

Fig. 3-15: Implementation of BSIM4 within Microwind2

The general equation of the threshold voltage is presented below.

$$vth = VTHO + K1 \cdot \sqrt{(\Phi_s - Vbs - \sqrt{\Phi_s})} - K2 \cdot Vbs + \Delta Vt_{SCE} + \Delta Vt_{NULD} + \Delta Vt_{DIBL}$$

where VTHO is the long channel threshold voltage at **Vbs=0** (Around 0.5V), K1 is the first order body bias coefficient (0.5 V<sup>1/2</sup>),  $\Phi$ s is the surface potential, *Vbs* is the bulk-source voltage, K2 is the second order body bias coefficient,  $\Delta$ Vt<sub>SCE</sub> is the short channel effect on *Vt*,  $\Delta$ Vt<sub>NULD</sub> is the non-uniform lateral doping effect, and  $\Delta$ Vt<sub>DIBL</sub> is the drain-induced barrier lowering effect of short channel on *Vt*.

Concerning the formulations for mobility of channel carriers, he generic parameter is U0, the mobility of electrons and holes. The effective mobility  $\mu_{eff}$  is reduced due to several effects: the bulk polarization, and the gate voltage. The equation implemented in Microwind2 is the most recent mobility model proposed in BSIM4.

$$\mu_{\mathit{eff}} = \frac{\mathtt{U0}}{1 + (\mathtt{UA} + \mathtt{UC.V}_{\mathtt{bseff}})(\frac{\mathtt{V}_{\mathtt{gsteff}} + 2(\mathtt{VTH0} - \mathtt{V}_{\mathtt{fb}} - \phi_{\mathtt{s}})}{\mathtt{TOXE}})^{\mathtt{EU}}}$$

where

- U0 is the low field mobility, in m<sup>2</sup>/V-s. Its default value is around 0.06 for n-channel MOS and 0.025 for p-channel MOS.

- UA is the first order mobility degradation coefficient, in m/V. Its default value is around 10<sup>-15</sup>.

- UC is the body-effect coefficient of mobility degradation, in  $m/V^2$ . Its default value is  $-0.045 \times 10^{-15}$ .

- VFB is the flat band voltage, in V.

- TOXE is the oxide thickness, in m. A typical value for TOXE in 0.12μm is 3nm (3.10<sup>-9</sup>m).

- EU is a coefficient equal to 1.67 for n-channel MOS, and 1.0 for p-channel MOS.

The current *Ids* is computed using one single equation, as described below.

$$Ids0 = \frac{Weff}{Leff} \mu eff \frac{\varepsilon_{0} \varepsilon_{r}}{\text{TOXE}} V_{gsteff} (1 - \frac{A_{bulk} V_{dseff}}{(2V_{gsteff} + 4.vt)}) \frac{V_{dseff}}{(1 + \frac{V_{dseff}}{\varepsilon_{sat} L_{eff}})}$$

| Parameter | Description                                                                                | NMOS value in          | NMOS value in          |

|-----------|--------------------------------------------------------------------------------------------|------------------------|------------------------|

|           |                                                                                            | 0.12μm                 | 0.12μm                 |

| VTHO      | Long channel threshold voltage at Vbs = 0V                                                 | 0.3V                   | 0.3V                   |

| VFB       | Flat-band voltage                                                                          | -0.9                   | -0.9                   |

| K1        | First-order body bias coefficient                                                          | 0.45 V1/2              | 0.45 V1/2              |

| K2        | Second-order body bias coefficient                                                         | 0.1                    | 0.1                    |

| LPE0      | Lateral non-uniform doping parameter at $Vbs = 0$                                          | 2.3°-10                | 2.3°-10                |

| DVT0      | First coefficient of short-channel effect on threshold voltage                             | 2.2                    | 2.2                    |

| DVT1      | Second coefficient of short-channel effect on Vth                                          | 0.53                   | 0.53                   |

| ETA0      | Drain induced barrier lowering coefficient                                                 | 0.08                   | 0.08                   |

| NFACTOR   | Sub-threshold turn-on swing factor. Controls the exponential increase of current with Vgs. | 1                      | 1                      |

| U0        | Low-field mobility                                                                         | 0.060 m2/Vs            | 0.025 m2/Vs            |

| UA        | Coefficient of first-order mobility degradation due to vertical field                      | 11.0e-15 m/V           | 11.0e-15 m/V           |

| UC        | Coefficient of mobility degradation due to body-<br>bias effect                            | -0.04650e-15 V-1       | -0.04650e-15 V-1       |

| VSAT      | Saturation velocity                                                                        | 8.0e4 m/s              | 8.0e4 m/s              |

| WINT      | Channel-width offset parameter                                                             | 0.01 <sup>e</sup> -6μm | 0.01 <sup>e</sup> -6μm |

| LINT      | Channel-length offset parameter                                                            | 0.01 <sup>e</sup> -6μm | 0.01 <sup>e</sup> -6μm |

| PSCBE1    | First substrate current induced body-effect mobility reduction                             | 4.24e8 V/m             | 4.24e8 V/m             |

| PSCBE2    | Second substrate current induced body-effect mobility reduction                            | 4.24e8 V/m             | 4.24e8 V/m             |

| KT1       | Temperature coefficient of the threshold voltage.                                          | -0.1V                  | -0.1V                  |

| UTE       | Temperature coefficient for the zero-field mobility -1.5 U0.                               |                        | -1.5                   |

| VOFF      | Offset voltage in subthreshold region.                                                     | -0.08V                 | -0.08V                 |

| PCLM      | Parameter for channel length modulation                                                    | 1.2                    | 1.2                    |

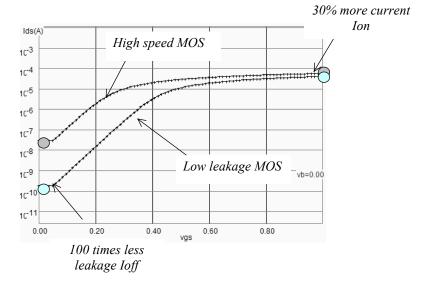

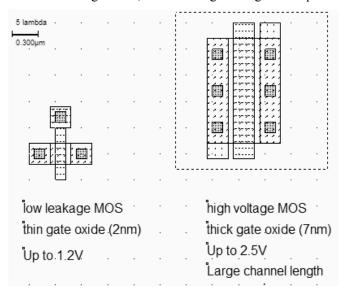

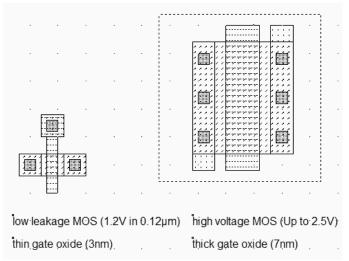

#### 3.13 Low leakage MOS

A new kind of MOS device has been introduced in deep submicron technologies, starting the 0.18µm CMOS process generation. The new MOS, called high speed MOS (HS) is available as well as the normal one, recalled Low leakage MOS (LL). The main objective is to propose two types of devices, one which reduces significantly the leakage current (LL version), that is the small current *loff* that flows from between drain and source with a gate voltage 0 (Supposed to be no current in first order approximation). On the figure below, the low leakage MOS device (right side) has an *loff* current reduced by a factor 100, thanks to a higher threshold voltage (0.4V rather than 0.3V).

Fig. 3-16: Low leakage MOS for lower Ioff current

The main drawback of the Low leakage MOS device is a 30% reduction of the *Ion* current, leading to a slower switching. High speed MOS devices should be used in the case of fast operation linked to critical nodes, while low leakage MOS should be placed whenever possible, for all nodes where a maximum switching speed is not required.

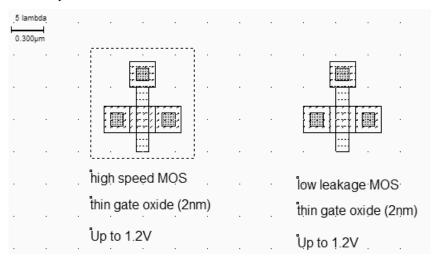

Fig. 3-17: High speed and Low leakage MOS layout. The only difference is the option layer to setup the high speed option

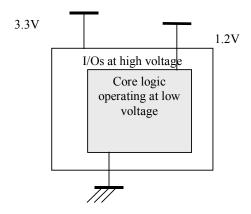

#### 3.14 High voltage MOS

Integrated circuits with low voltage internal supply and high voltage I/O interface are getting common in deep sub-micron technology. The internal logic of the integrated circuit operates at very low voltage (Typically 1.0V in  $0.12\mu m$ ), while the I/O devices operate in standard voltages (2.5, 3.3 or 5V). The

input/output structures work at high voltage thanks to specific MOS devices with thick oxide, while the internal devices work at low voltage with optimum performances.

Fig. 3-18: Interfacing low voltage logic signals with high voltage I/Os requires specific circuits operating in high voltage mode.

For I/Os operating at high voltage, specific MOS devices called "High voltage MOS" are used. We cannot use high-speed or low leakage devices as their oxide is too small. A 2.5V voltage would damage the gate oxide of a high-speed MOS in 0.12µm technology. The high voltage MOS is built using a thick oxide, two to three times thicker than the low voltage MOS, to handle high voltages as required by the I/O interfaces.

Fig. 3-19: low leakage and high voltage MOS. The high voltage MOS has a minimum length longer than for the other MOS. The gate oxide is also thicker to handle high voltage operation.

#### 3.15 Temperature effects on the MOS

Three main parameters are concerned by the sensitivity to temperature: the threshold voltage VTO, the mobility U0 and the slope in sub-threshold mode. Both VTO and U0 decrease when the temperature increases. The modeling of the temperature effect in BSIM4 is as follows. In Microwind2, TNOM is fixed to

$300^{\circ}$ K, equivalent to  $27^{\circ}$ C. UTE is negative, and set to -1.8 in  $0.12\mu m$  CMOS technology, while KT1 is set to -0.06 by default.

$$U0 = U0_{(T=27)} \left(\frac{T+273}{TNOM}\right)^{UTE}$$

(3-45)

$$VT = VT0_{(T=27)} + KT1(\frac{T+273}{TNOM} - 1)$$

(3-46)

A higher temperature leads to a reduced mobility, as UTE is negative. Consequently, at a higher temperature, the current *Ids* is lowered.

Fig. 3-20. Effect of temperature on the MOS device characteristics

To obtain the curve of figure 3-20, proceed as follows:

- Click the icon MOS characteristics

- Select one MOS in the design or click anywhere

- Select the curve Id/Vg

• Enable the screen memory mode by a click on this icon.

Change the temperature. The change in the slope is shown. You may reduce the number of *Id* curves by putting a 0.0 in the field **For Vb from 0 to.**

In Microwind2, you can also get access to temperature using the command **Simulate→Simulation**Parameters. The screen below appears. The temperature is given in °C.

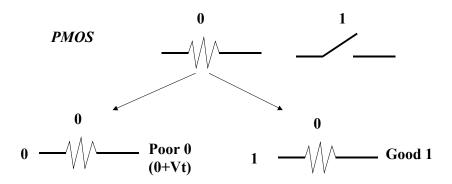

#### 3.16 The PMOS Transistor

The p-channel transistor simulation features the same functions as the n-channel device, but with opposite voltage control of the gate. For the nMOS, the channel is created with a logic 1 on the gate. For the pMOS, the channel is created for a logic 0 on the gate. Load the file pmos.msk and click the icon MOS characteristics. The p-channel MOS simulation appears, as shown in Figure 3-21. Note that the pMOS gives approximately half of the maximum current given by the nMOS with the same device size. The highest current is obtained with the lowest possible gate voltage, that is 0.

Fig. 3-21. Layout and simulation of the p-channel MOS (pMOS.MSK)

From the simulation of figure 3-21, we see that the pMOS device is able to pass well the logic level 1. But the logic level 0 is transformed into a positive voltage, equal to the threshold voltage of the MOS device. The summary of the p-channel MOS performances is reported in figure 3-20.

Fig. 3-22. Summary of the performances of a pMOS device

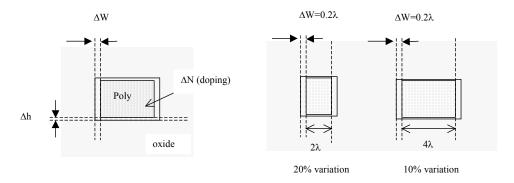

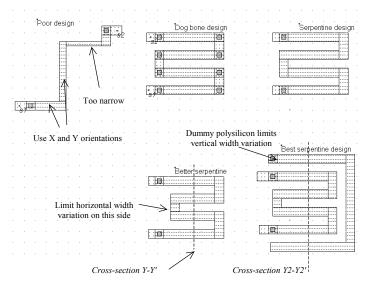

#### 3.17 Process Variations

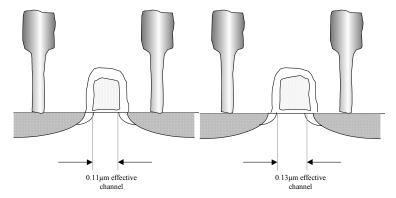

The simulated results should not be considered as absolute values. Due to unavoidable process variations during the hundreds of chemical steps for the fabrication of the integrated circuit, the MOS characteristics are never exactly identical from one device to another, and from one die to an other. It is very common to measure 5% to 20% electrical difference within the same die. In figure 3-23, although both devices have been designed with a drawn 2 lambda, the result is a 0.11µm length for the MOS situated on the left side, and 0.13µm for the MOS situated on the right side.

Fig. 3-23: The same MOS device may be fabricated with an important effective channel variation

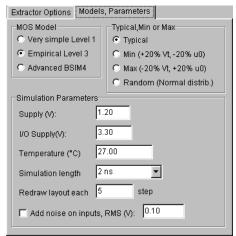

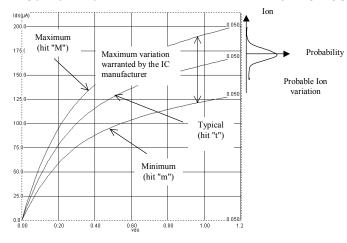

The menu **Simulate Simulation parameters** gives a simple access to minimum/typical/maximum parameter sets. The approach has consisted in altering two main parameters: the threshold voltage (20% random variation, Gaussian distribution) and the mobility (20% random variation). All other parameters are supposed to be constant.

Fig. 3-24: Access to minimum, typical, maximum model parameters or Random simulation

A comparative simulation of the *Id/Vd* curve in typical, maximum and minimum scenarios shows a very large variation of performances (Figure 3-25). The user may automatically switch from one parameter set to an other by a press of a key ("M" for maximum, "m" for minimum, "t" for typical).

#### 3. The MOS device

Fig. 3-25: The MOS Id/vd curve in Min, Typ, Max modes.

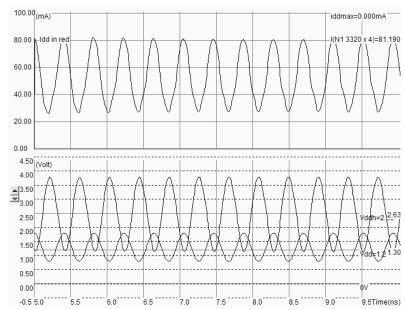

#### 3.18 The Transmission Gate

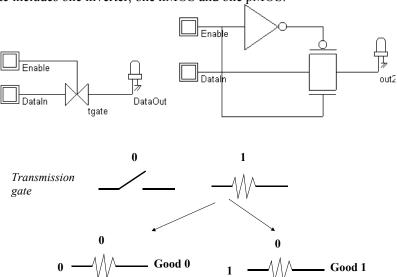

Both NMOS devices and PMOS devices exhibit poor performances when transmitting one particular logic information. The nMOS degrades the logic level 1, the pMOS degrades the logic level 0. Thus, a perfect pass gate can be constructed from the combination of nMOS and pMOS devices working in a complementary way, leading to improved switching performances. Such a circuit, presented in figure 3-26, is called the transmission gate. In DSCH2, the symbol may be found in the **Advance** menu in the palette. The transmission gate includes one inverter, one nMOS and one pMOS.

Fig. 3-26. Schematic diagram of the transmission gate (Tgate.SCH)

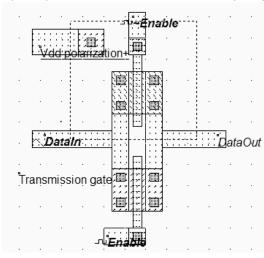

Fig. 3-27. Layout of the transmission gate (TGATE.MSK)

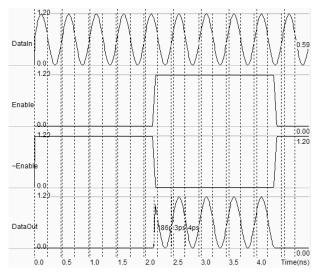

The layout of the transmission gate is reported in figure 3-27. The n-channel MOS is situated on the bottom the p-channel MOS on the top. Notice that the gate controls are not connected, as ~*Enable* is the opposite of *Enable*. The operation of the transmission gate is illustrated in figure 3-24. A sinusoidal wave with a frequency of 2GHz is assigned to *DataIn*. With a zero on *Enable* (And a 1 on ~*Enable*), the switch is off, and no signal is transferred. When *Enable* is asserted, the sinusoidal wave appears nearly identical to the output.

Fig. 3-24. Simulation of the transmission gate (TGATE.MSK)

# 4 The Inverter

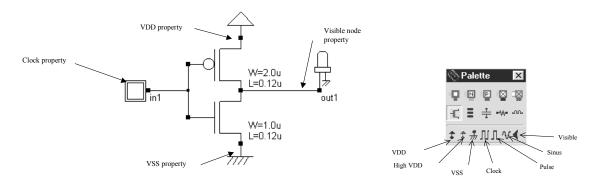

This chapter describes the CMOS inverter at logic level, using the logic editor and simulator DSCH2, and at layout level, using the tool MICROWIND2.

#### 4.1 The Logic Inverter

In this section, an inverter circuit is loaded and simulated. Click **File Open** in the main menu. Select INV.SCH in the list. In this circuit are one button situated on the left side of the design, the inverter and a led. Click **Simulate Start simulation** in the main menu.

Fig. 4.1: The schematic diagram including one single inverter (Inverter.SCH)

Now, click inside the buttons situated on the left part of the diagram. The result is displayed on the leds. The red value indicates logic 1, the black value means a logic 0. Click the button **Stop simulation** shown in the picture below. You are back to the editor.

Fig. 4.2: The button Stop Simulation

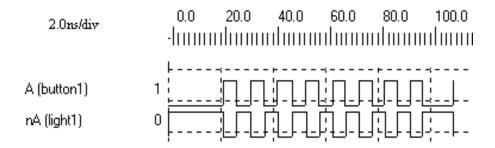

Click the **chronogram** icon to get access to the chronograms of the previous simulation (Figure 4-3). As seen in the waveform, the value of the output is the logic opposite of that of the input.

33

Fig. 4-3 Chronograms of the inverter simulation (CmosInv.SCH)

Double click on the INV symbol, the symbol properties window is activated. In this window appears the VERILOG description (left side) and the list of pins (right side). A set of drawing options is also reported in the same window. Notice the gate delay (0.03ns in the default technology), the fanout that represents the number of cells connected to the output pin (1 cell connected), and the wire delay due to this cell connection (An extra 0.140ns delay).

#### 4.2 THE CMOS INVERTER

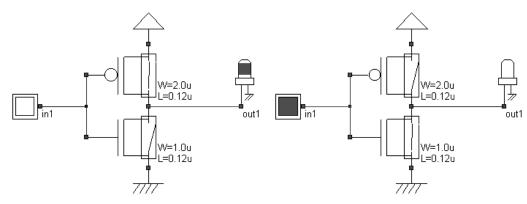

The CMOS inverter design is detailed in the figure below. Here the p-channel MOS and the n-channel MOS transistors function as switches. When the input signal is logic 0 (Fig. 4-3 left), the nMOS is switched off while PMOS passes VDD through the output. When the input signal is logic 1 (Fig. 4-3 right), the pMOS is switched off while the nMOS passes VSS to the output.

Fig. 4-3: The MOS Inverter (File CmosInv.sch)

The fanout corresponds to the number of gates connected to the inverter output. Physically, a large fanout means a large number of connections, that is a large load capacitance. If we simulate an inverter loaded with one single output, the switching delay is small. Now, if we load the inverter by several outputs, the delay and the power consumption are increased. The power consumption linearly increases with the load capacitance. This is mainly due to the current needed to charge and discharge that capacitance.

#### 4.3 MANUAL LAYOUT OF THE INVERTER

In this paragraph, the procedure to create manually the layout of a CMOS inverter is described. Click the icon **MOS generator** on the palette. The following window appears. By default the proposed length is the minimum length available in the technology (2 lambda), and the width is 10 lambda. In 0.12μm technology, where lambda is 0.06μm, the corresponding size is 0.12μm for the length and 0.6μm for the width. Simply click **Generate Device**, and click on the middle of the screen to fix the MOS device.

Click again the icon **MOS generator** on the palette. Change the type of device by a tick on **p-channel**, and click **Generate Device**. Click on the top of the nMOS to fix the pMOS device. The result is displayed in figure 4-4.

Fig. 4-4. Selecting the nMOS device

#### 4.4 Connection between Devices

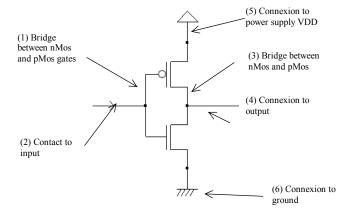

Fig. 4-5 Connections required to build the inverter (CmosInv.SCH)

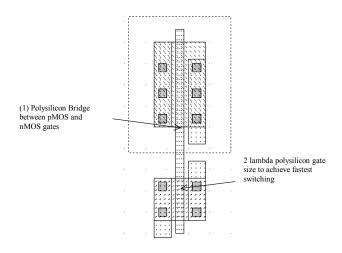

Within CMOS cells, metal and polysilicon are used as interconnects for signals. Metal is a much better conductor than polysilicon. Consequently, polysilicon is only used to interconnect gates, such as the bridge (1) between pMOS and nMOS gates, as described in the schematic diagram of figure 4-5. Polysilicon is rarely used for long interconnects, except if a huge resistance value is expected.

In the layout shown in figure 4-5, the polysilicon bridge links the gate of the n-channel MOS with the gate of the p-channel MOS device. The polysilicon serves as the gate control and the bridge between MOS gates.

Fig. 4-5 Polysilicon bridge between nMOS and pMOS devices (InvSteps.MSK)

#### 4.5 Useful Editing Tools

The following commands may help you in the layout design and verification processes.

| Command                     | Icon/Short cut | Menu          | Description                                                                  |

|-----------------------------|----------------|---------------|------------------------------------------------------------------------------|

| UNDO                        | CTRL+U         | Edit menu     | Cancels the last editing operation                                           |

| DELETE                      | CTRL+X         | Edit menu     | Erases some layout included in the given area or pointed by the mouse.       |

| STRETCH                     | <b>6</b>       | Edit menu     | Changes the size of one box, or moves the layout included in the given area. |

| COPY                        | CTRL+C         | Edit Menu     | Copies the layout included in the given area.                                |

| VIEW<br>ELECTRICA<br>L NODE | CTRL+N         | View Menu     | Verifies the electrical net connections.                                     |

| 2D CROSS-<br>SECTION        | 2              | Simulate Menu | Shows the aspect of the circuit in vertical cross-section.                   |

Table 4-1: A set of useful editing tools

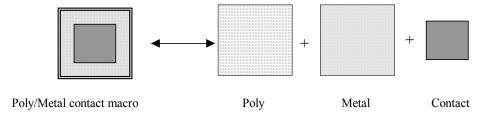

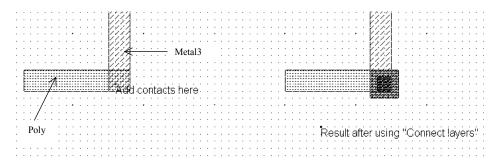

## 4.6 Metal-to-poly

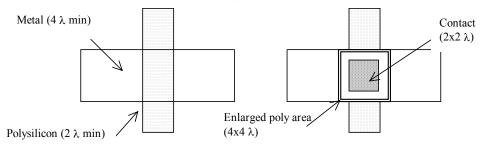

As polysilicon is a poor conductor, metal is preferred to interconnect signals and supplies. Consequently, the input connection of the inverter is made with metal. Metal and polysilicon are separated by an oxide which prevents electrical connections. Therefore, a box of metal drawn across a box of polysilicon does not allow an electrical connection (Figure 4-6). To build an electrical connection, a physical contact is needed. The corresponding layer is called "contact". You may insert a metal-to-polysilicon contact in the layout using a direct macro situated in the palette.

Fig. 4-6 Physical contact between metal and polysilicon

Fig. 4-7 Adding a poly contact, poly and metal bridges to construct the CMOS inverter (InvSteps.MSK)

The *Process Simulator* shows the vertical aspect of the layout, as when fabrication has been completed. This feature is a significant aid to understand the circuit structure and the way layers are stacked on top of each other. A click of the mouse on the left side of the n-channel device layout and the release of the mouse at the right side give the cross-section reported in figure 4-8.

Fig.4-8 The 2D process section of the inverter circuit near the nMOS device (InvSteps.MSK)

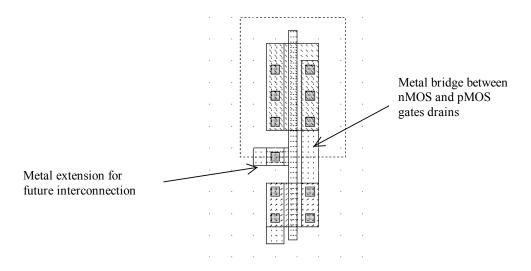

## 4.7 Supply Connections

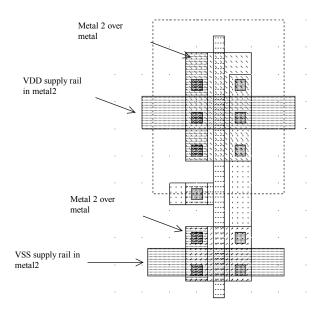

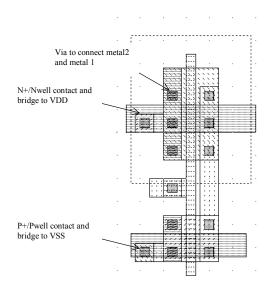

The next design step consists in adding supply connections, that is the positive supply VDD and the ground supply VSS. In figure 4-9, we use the metal2 layer (Second level of metallization) to create horizontal supply connections. Notice that the metal connections have a large width. This is because a strong current may flow within these supply interconnects. Enlarging the supply metal lines reduces the resistance and avoids electrical overstress.

Fig.4-9 Adding metal2 supply lines and the appropriate vias (InvSteps.MSK)

The simplest way to build the physical connection is to add a metal/Metal2 contact that may be found in the palette. The connection is created by a plug called "via" between metal2 and metal layers.

The final layout design step consists in adding polarization contacts. These contacts convey the VSS and VDD voltage supply close to the bulk regions of the device. Remember that the n-well region should always be polarized to a high voltage to avoid short-circuit between VDD and VSS. Adding the VDD polarization in the n-well region is a very strict rule.

Fig.4-10 Adding polarization contacts

#### 4.8 Process steps to build the Inverter

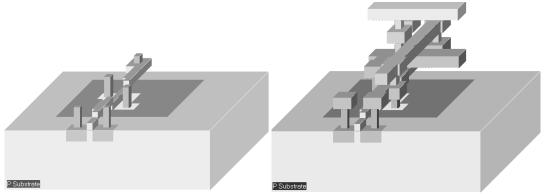

At that point, it might be interesting to illustrate the steps of fabrication as they would sequence in a foundry. Microwind includes a 3D process viewer for that purpose. Click **Simulate**  $\rightarrow$  **Process steps in 3D**. The simulation of the CMOS fabrication process is performed, step by step by a click on **Next Step**. On figure 4-11, the picture on the left represents the nMOS device, pMOS device, common polysilicon gate and contacts. The picture on the right represents the same portion of layout with the metal layers stacked on top of the active devices.

Fig.4-11 The step-by-step fabrication of the Inverter circuit (InvSteps.MSK)

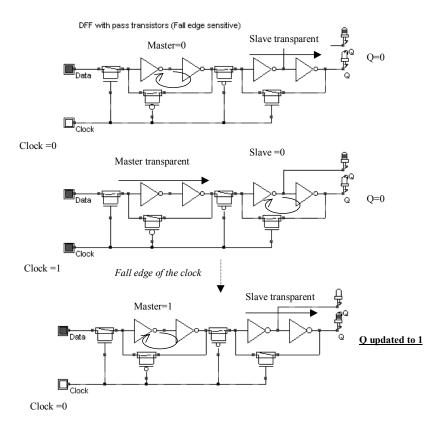

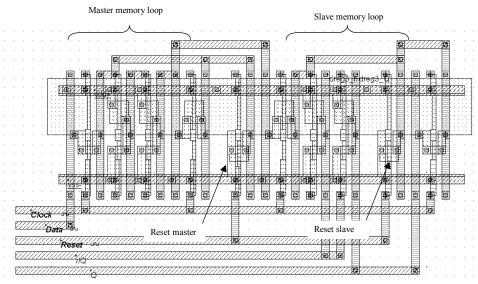

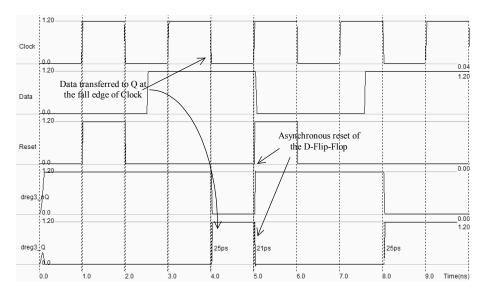

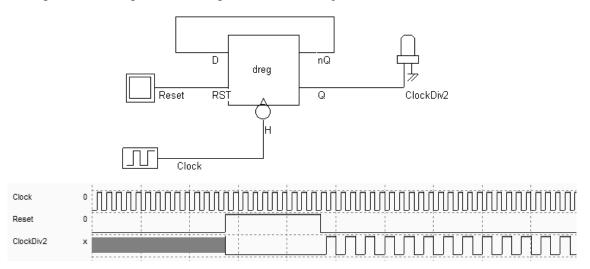

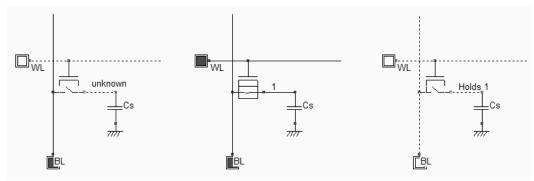

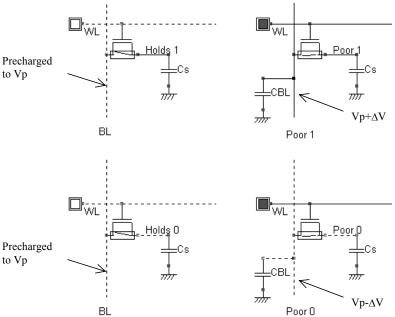

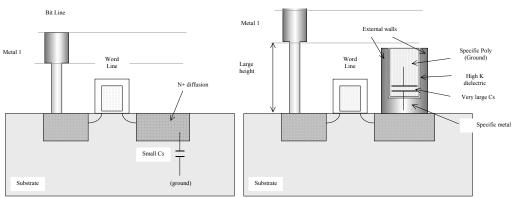

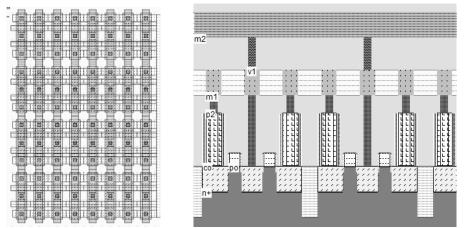

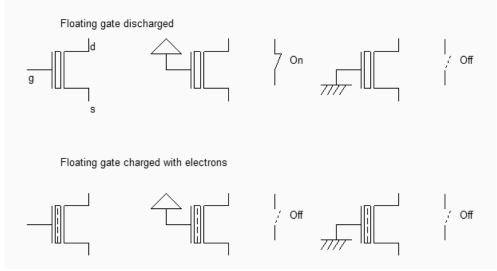

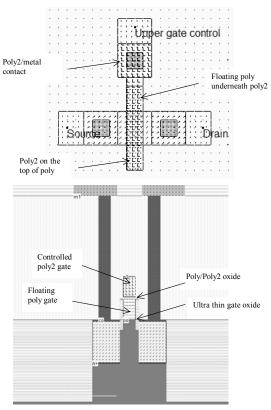

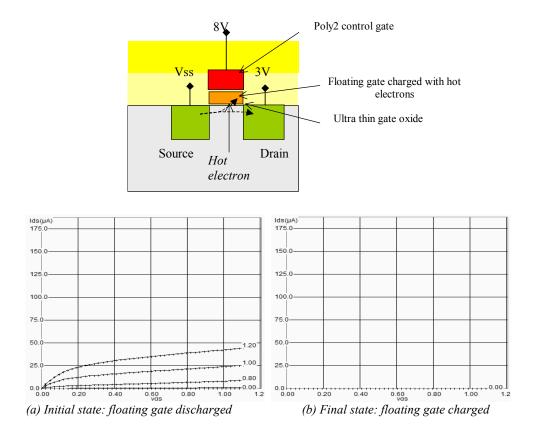

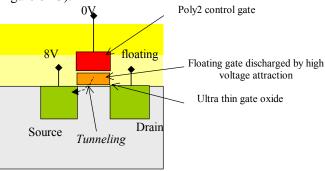

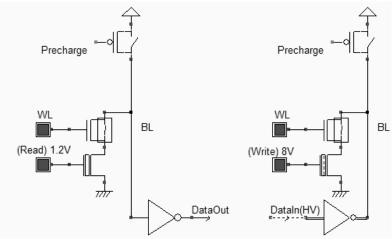

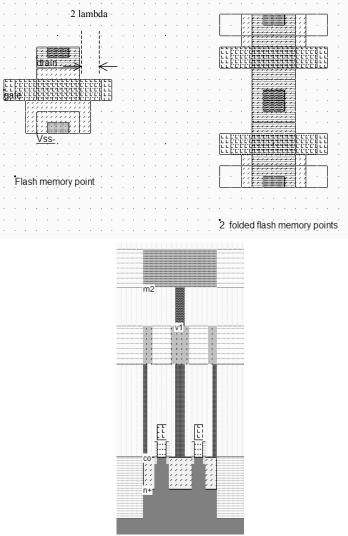

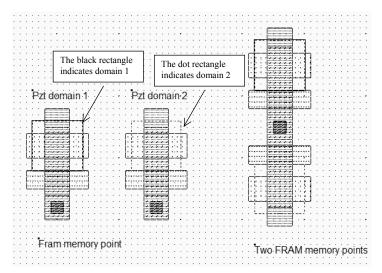

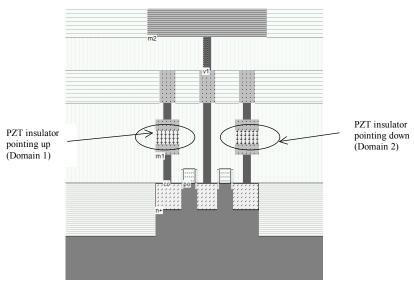

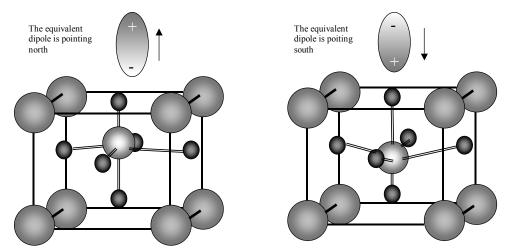

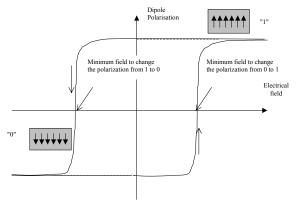

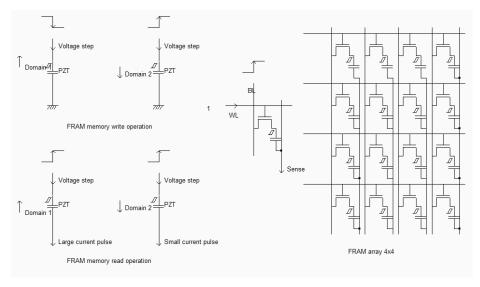

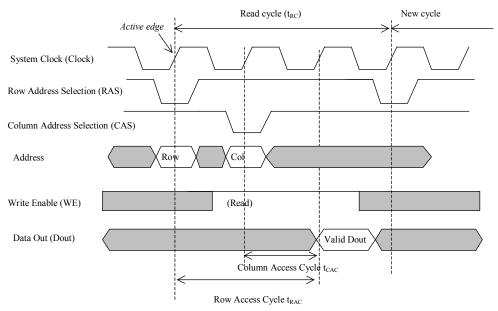

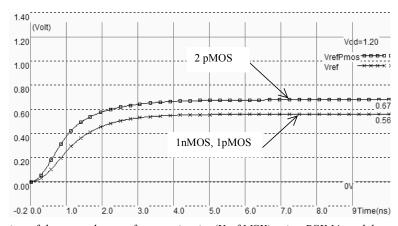

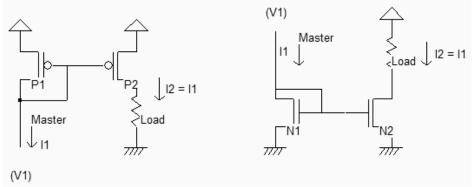

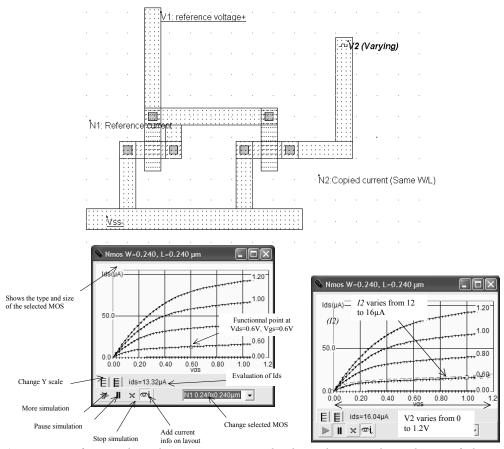

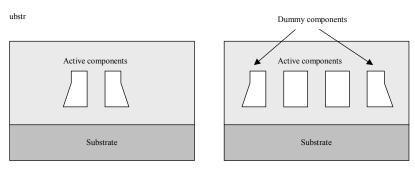

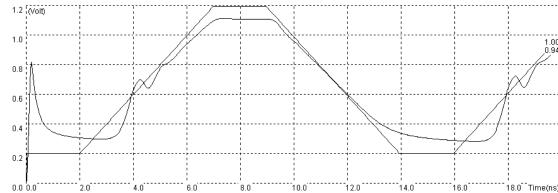

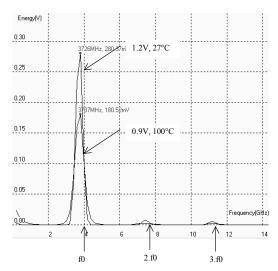

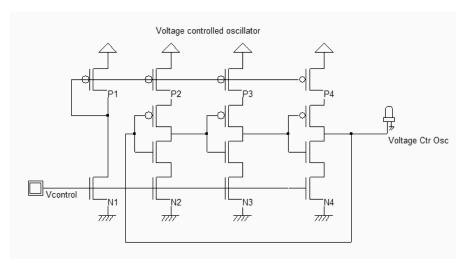

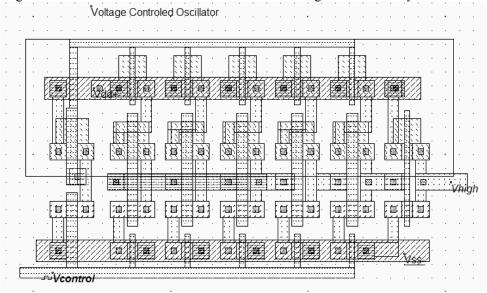

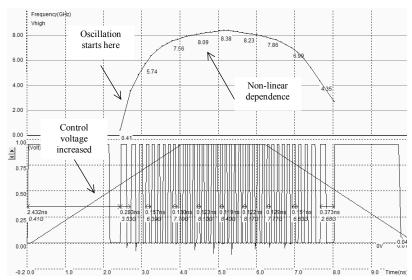

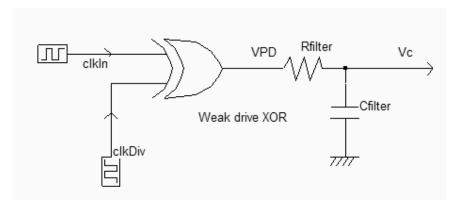

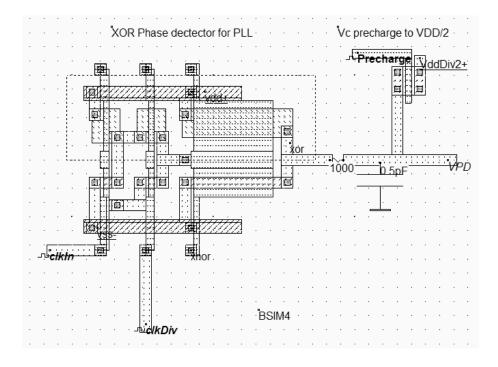

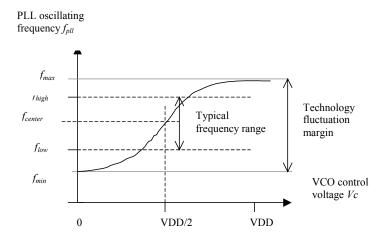

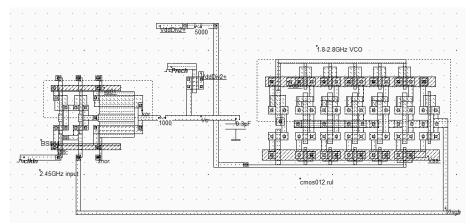

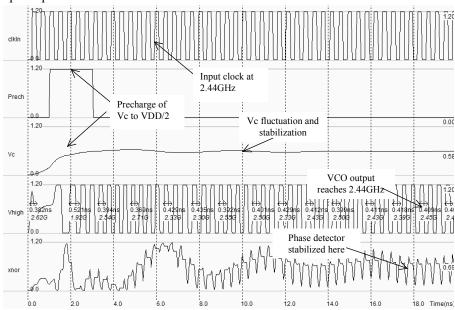

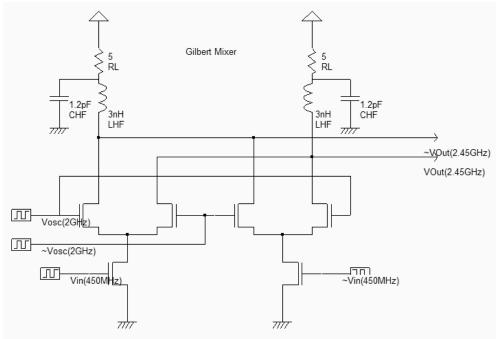

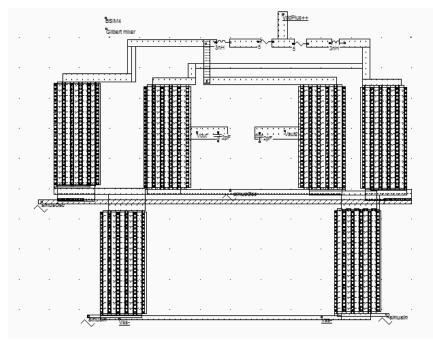

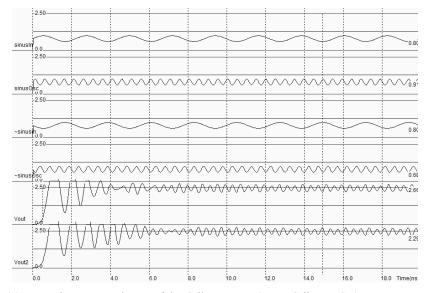

#### 4.9 Inverter Simulation